## **TUM ACADEMIC SALON 2022**

## The paradigm shift in automotive zonal gatewaying

How to elevate the E/E architecture from good to great: elastic network SoC propelled by HW innovation

<u>Francesc Fons</u>, Angela Gonzalez Mariño, Abdoul Aziz Kane **Automotive Engineering Lab, Huawei Munich Research Center** TUM Garching (Munich), 30.09.2022

# Contents

# **1.** [WHY] Automotive Electronic Industry

- The Innovation Race

- Pain Points & Challenges

# 2. [HOW] IVN, Zonal GW Controller & Networking Chipset

- Huawei Automotive IVN Research Group

- Zonal Gateway Controller

- Network SoC Prototyping

# 3. [WHAT] Elastic Gateway SoC (eGW) Concept

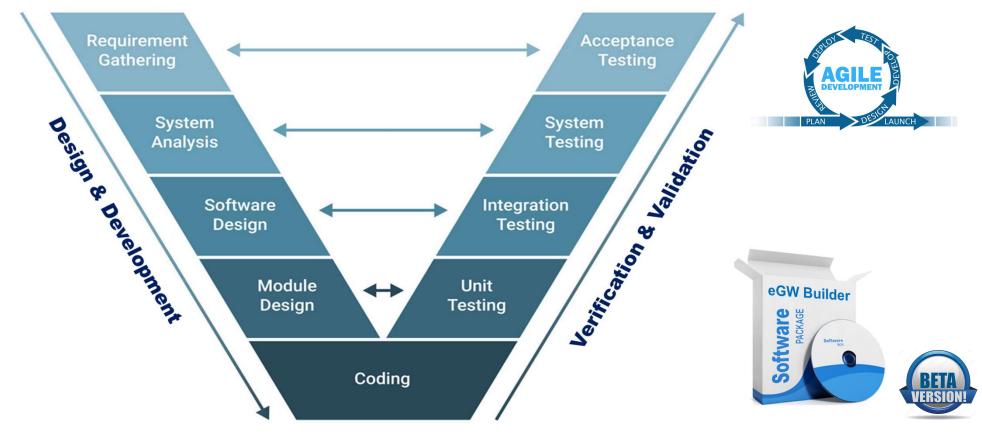

- Related Art on HW/SW Codesign in Automotive

- The 12 HW Innovations on NW & APP Processing of eGW SoC

# Contents

# **1. [WHY] Automotive Electronic Industry**

- The Innovation Race

- Pain Points & Challenges

- 2. [HOW] IVN, Zonal GW Controller & Networking Chipset

- Huawei Automotive IVN Research Group

- Zonal Gateway Controller

- Network SoC Prototyping

# 3. [WHAT] Elastic Gateway SoC (eGW) Concept

- Related Art on HW/SW Codesign in Automotive

- The 12 HW Innovations on NW & APP Processing of eGW SoC

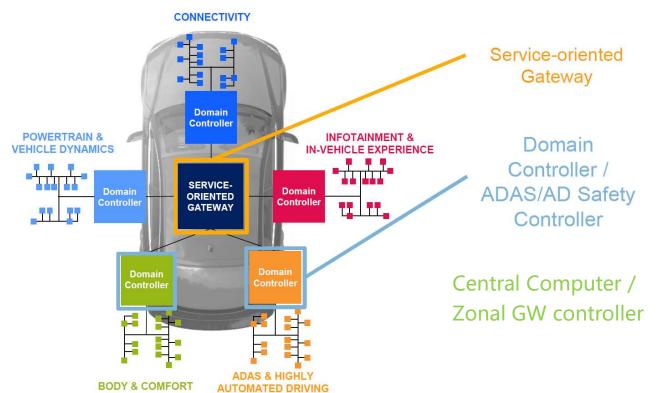

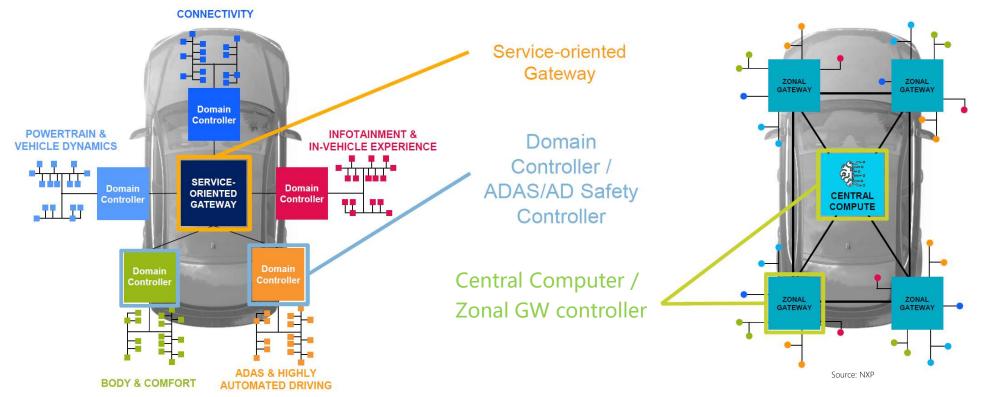

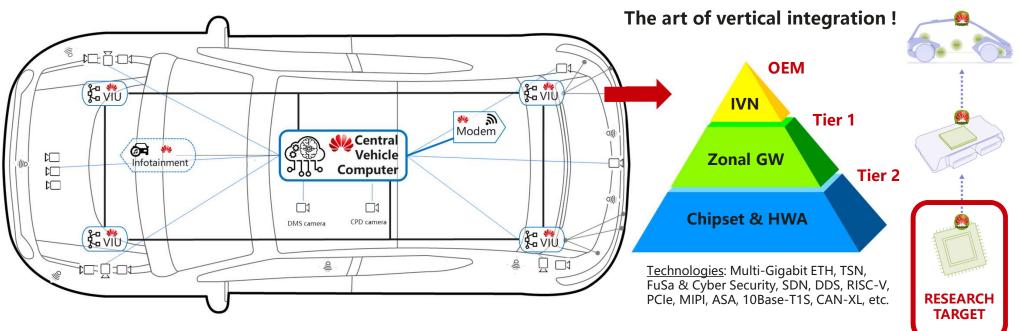

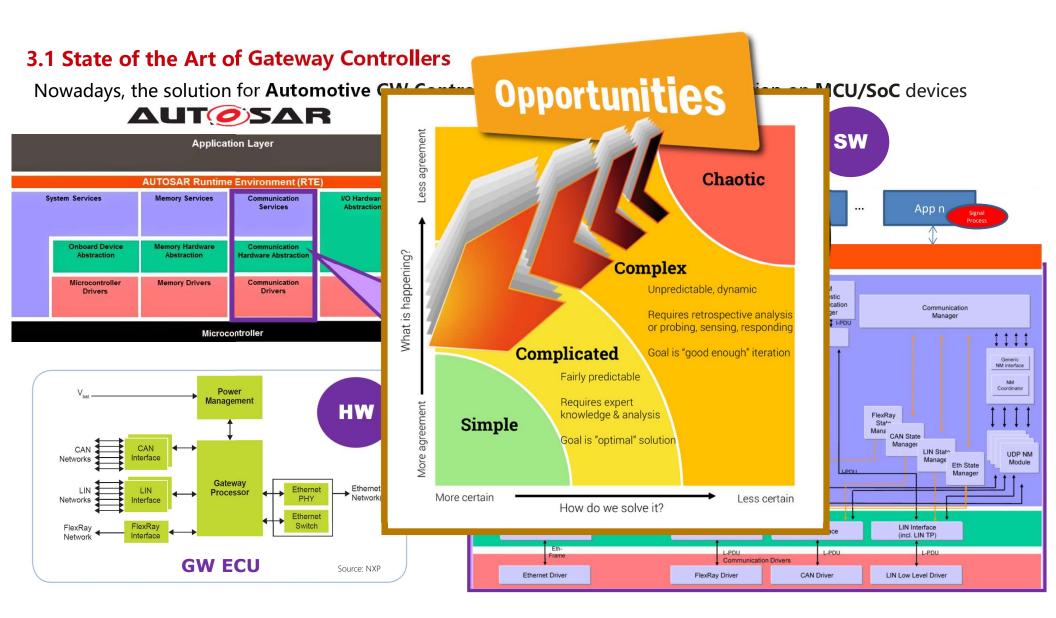

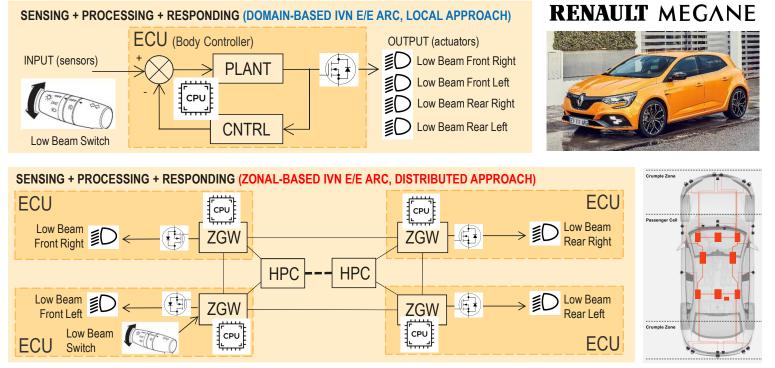

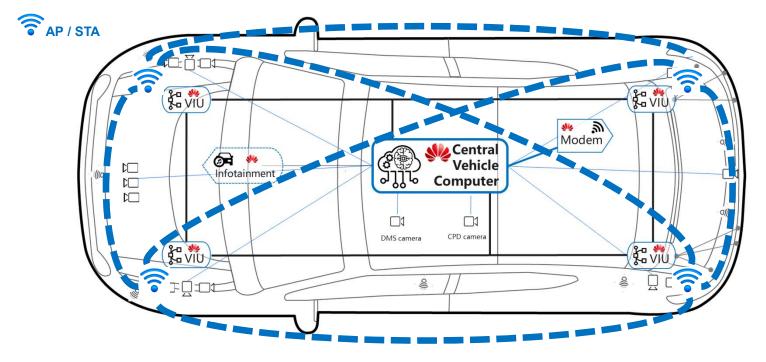

Nowadays, the **Automotive E/E Architecture** is being profoundly reshaped, in deep transformation -affecting especially the IVN infrastructure- in order to enable thus the **Autonomous-Connected-Electric-Shared (ACES) vehicle of tomorrow**

From DOMAIN-BASED E/E IVN ARCHITECTURE...

From **LOGICAL** distribution of functions (**Domain Controllers, ZGW & ECUs**)...

Nowadays, the **Automotive E/E Architecture** is being profoundly reshaped, in deep transformation -affecting especially the IVN infrastructure- in order to enable thus the **Autonomous-Connected-Electric-Shared (ACES) vehicle of tomorrow**

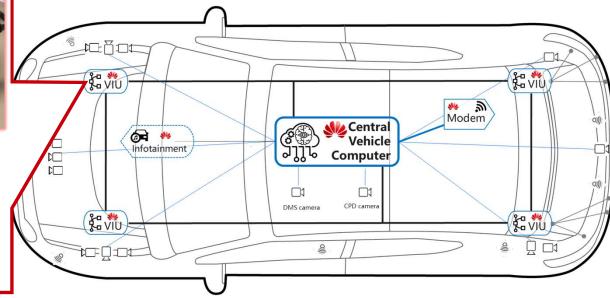

... to ZONE-BASED E/E IVN ARCHITECTURE

From LOGICAL distribution of functions (Domain Controllers, ZGW & ECUs)... ...to PHYSICAL (i.e. cross-domain) distribution (HPCs and Zonal GW Controllers)

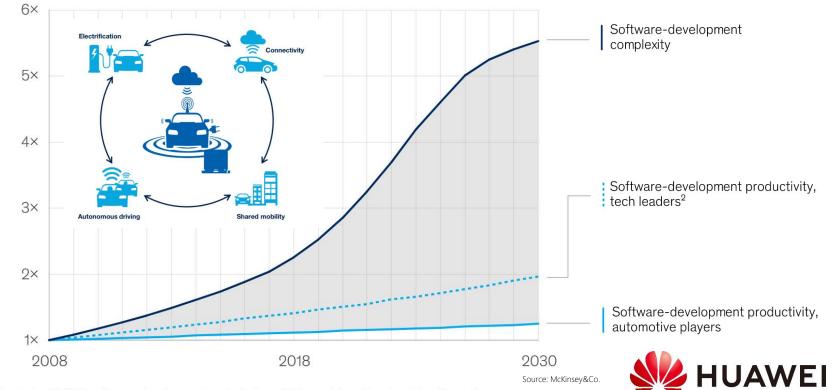

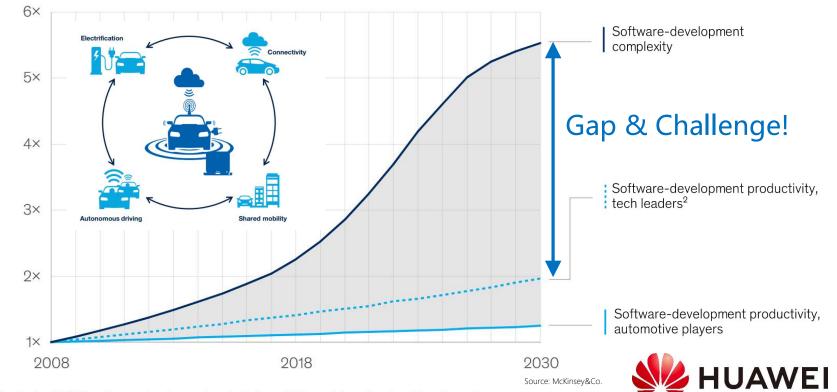

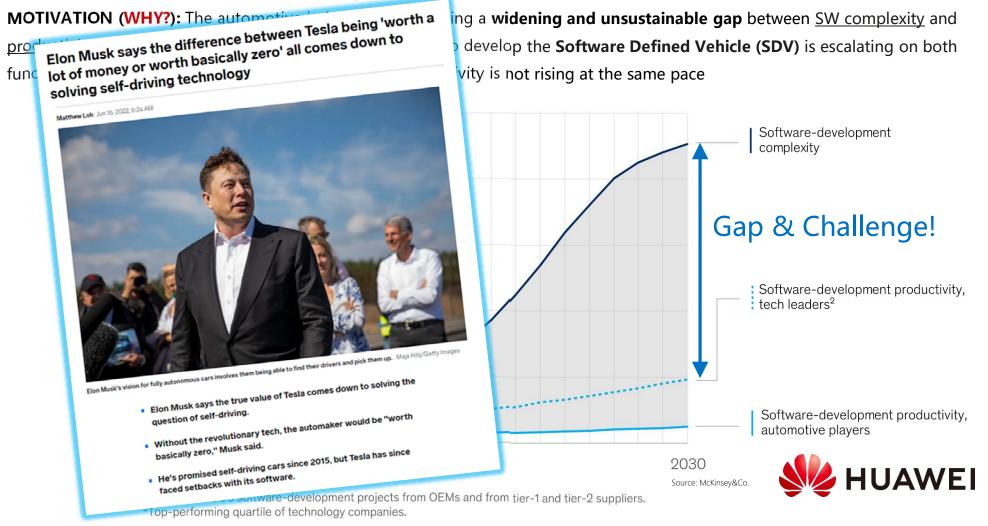

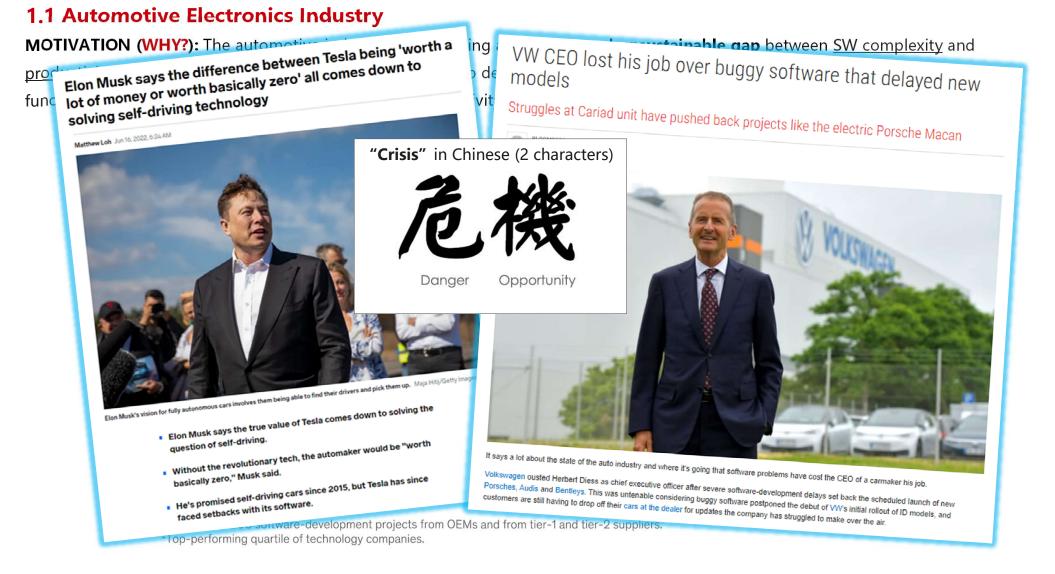

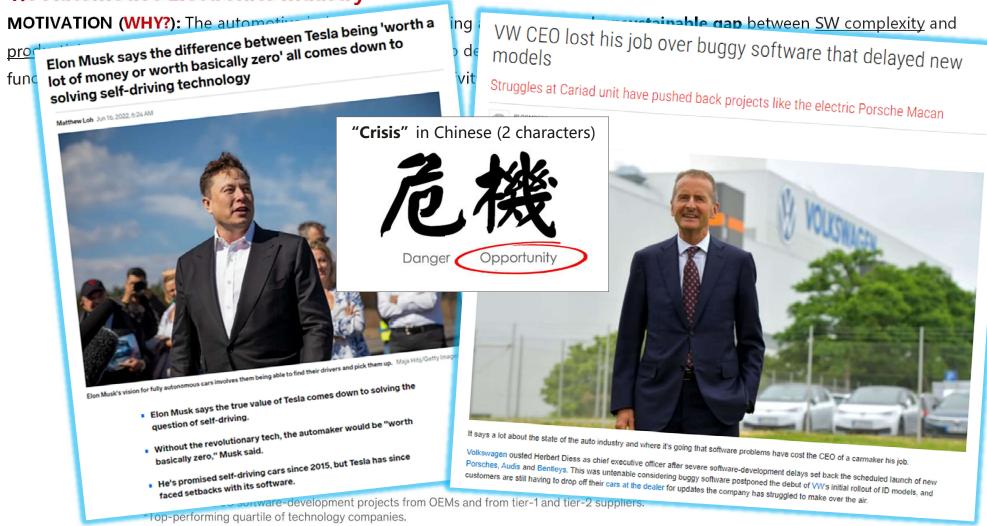

**MOTIVATION (WHY?):** The automotive industry is confronting a **widening and unsustainable gap** between <u>SW complexity</u> and <u>productivity levels</u>. The complexity of automotive software to develop the **Software Defined Vehicle (SDV)** is escalating on both functional and architectural levels, but development productivity is not rising at the same pace

<sup>1</sup>Analysis of >200 software-development projects from OEMs and from tier-1 and tier-2 suppliers. <sup>2</sup>Top-performing quartile of technology companies.

**MOTIVATION (WHY?):** The automotive industry is confronting a **widening and unsustainable gap** between <u>SW complexity</u> and <u>productivity levels</u>. The complexity of automotive software to develop the **Software Defined Vehicle (SDV)** is escalating on both functional and architectural levels, but development productivity is not rising at the same pace

<sup>1</sup>Analysis of >200 software-development projects from OEMs and from tier-1 and tier-2 suppliers. <sup>2</sup>Top-performing quartile of technology companies.

ing

and second secon

#### **1.1 Automotive Electronics Industry**

#### MOTIVATION (WHY?): The autometic

Elon Musk says the difference between Tesla being 'worth a func lot of money or worth basically zero' all comes down to

# Contents

# **1. [WHY] Automotive Electronic Industry**

- The Innovation Race

- Pain Points & Challenges

# 2. [HOW] IVN, Zonal GW Controller & Networking Chipset

- Huawei Automotive IVN Research Group

- Zonal Gateway Controller

- Network SoC Prototyping

- 3. [WHAT] Elastic Gateway SoC (eGW) Concept

- Related Art on HW/SW Codesign in Automotive

- The 12 HW Innovations on NW & APP Processing of eGW SoC

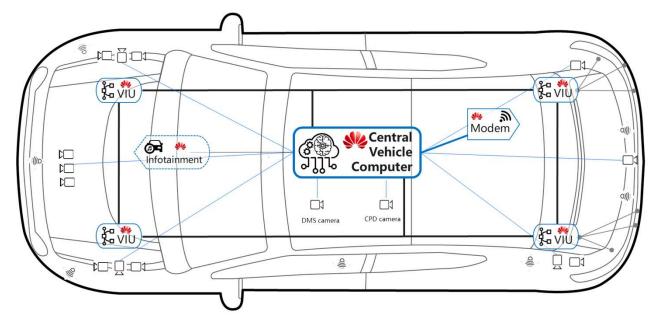

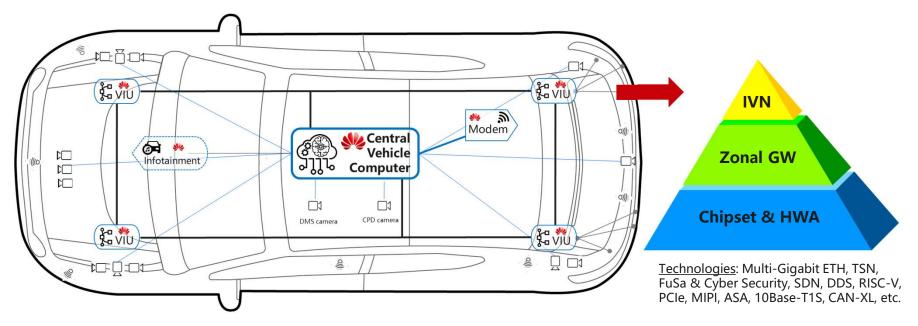

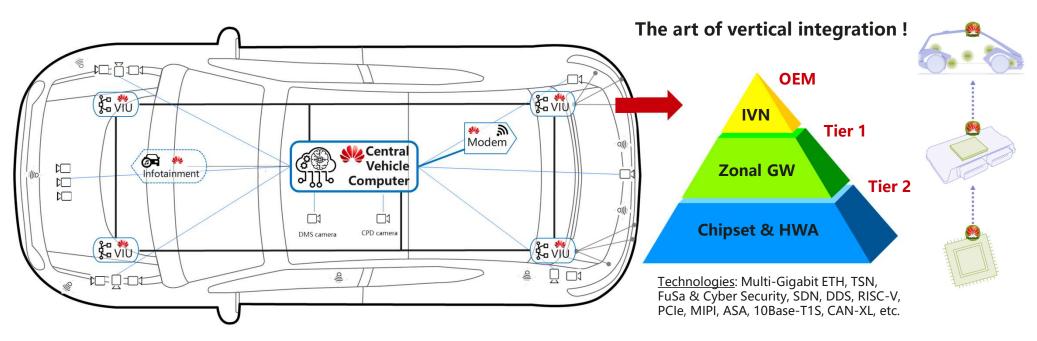

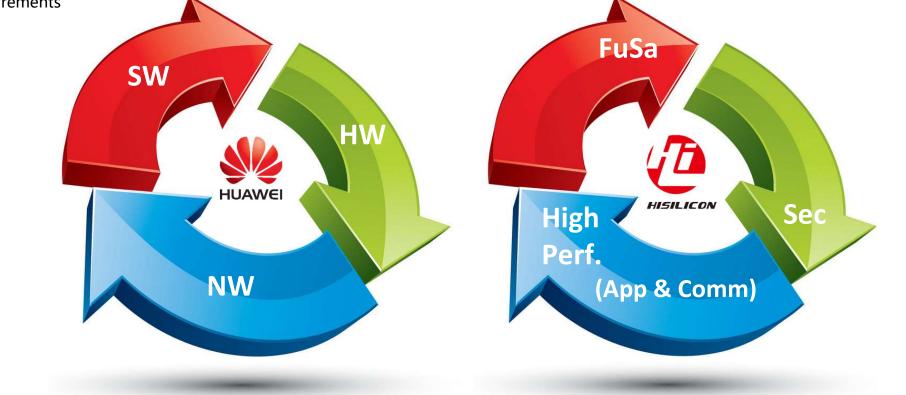

Our goal is to perform research, generate new knowledge and develop innovative technological solutions in the areas of:

- Automotive E/E IVN Architectures (System/Vehicle Level: NW)

- Zonal GW Controller Development (Component Level: HW/SW ECU)

- Network SoC and Hardware Accelerators Design (Chipset Level: SoC/HWA)

while validating them through hands-on deployment of Proof-of-Concepts (PoC) on rapid prototyping platforms (SoC/MCU/FPGA)

Our goal is to perform research, generate new knowledge and develop innovative technological solutions in the areas of:

- Automotive E/E IVN Architectures (System/Vehicle Level: NW)

- Zonal GW Controller Development (Component Level: HW/SW ECU)

- Network SoC and Hardware Accelerators Design (Chipset Level: SoC/HWA)

while validating them through hands-on deployment of Proof-of-Concepts (PoC) on rapid prototyping platforms (SoC/MCU/FPGA)

Our goal is to perform research, generate new knowledge and develop innovative technological solutions in the areas of:

- Automotive E/E IVN Architectures (System/Vehicle Level: NW)

- Zonal GW Controller Development (Component Level: HW/SW ECU)

- Network SoC and Hardware Accelerators Design (Chipset Level: SoC/HWA)

while validating them through hands-on deployment of **Proof-of-Concepts (PoC)** on rapid prototyping platforms (SoC/MCU/FPGA)

Our goal is to perform research, generate new knowledge and develop innovative technological solutions in the areas of:

- Automotive E/E IVN Architectures (System/Vehicle Level: NW)

- Zonal GW Controller Development (Component Level: HW/SW ECU)

- Network SoC and Hardware Accelerators Design (Chipset Level: SoC/HWA)

while validating them through hands-on deployment of Proof-of-Concepts (PoC) on rapid prototyping platforms (SoC/MCU/FPGA)

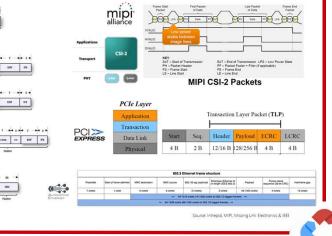

#### 2.2 Huawei Automotive In-Vehicle Network Research Group – Research Technologies

a 13 ala 2 ala 2 ala mipi (a) (a) lin Break SYNC ID PS 00 PH Data PP 00 CSI-+ 14 12 - He 6 He -----CAN o Arbitration Contro CRC Ack EDF IFS ----**MIPI CSI-2 Packets** Ack EOF IFS PCIe Layer Transaction Layer Packet (TLP) Application Transaction 2 - ++ 3 ++ 2 - ++ 3 + PCI> Start Seq. Header Data Link CONKL Reinte Au EOF 195 Physical 802.3 Ethernet frame a .... 802 1G top (optional) Etherhyte (Ethernet II) Payload MAC source Cycle ( 2 octets 4 ocherte Source: Intrepid, MIPI, Missing Link Electronics & IEEE

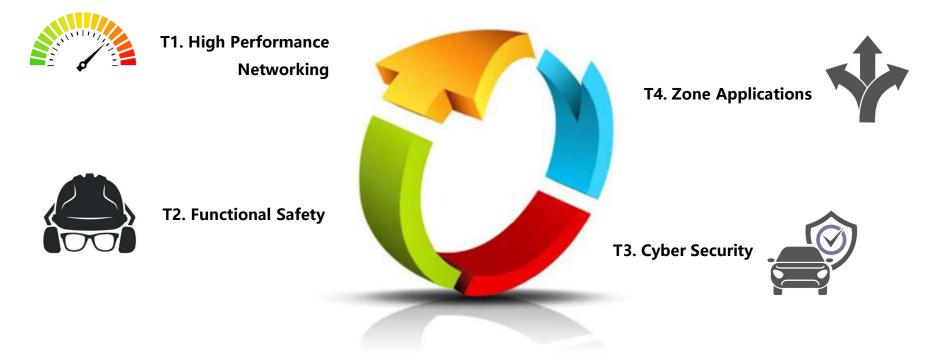

T1. High performance in Gatewaying/Tunneling/Routing/Forwarding processing is crucial (E2E latency, jitter, bandwidth, etc.)

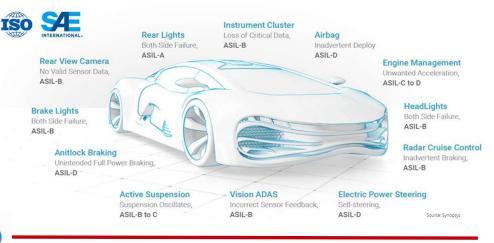

T2. Functional Safety is getting more and more attention in the ACES vehicle of tomorrow

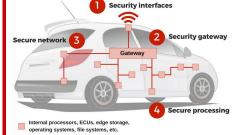

T3. Cyber Security, together with FuSa, deployed in the Zonal Gateway Controller is key in order to achieve a holistic security

Intrusion Detection and Prevention

T4. The deployment of Application Layer functionality in zonal GW controllers, on top of the IVN infrastructure, needs to guarantee right level of reliability, performance and cost-effectiveness

| Applications       | Powertrain/Chassis            | Body/Comfort                     | Cockpit/Infotainment | ADAS/AD     | Connectivity              |

|--------------------|-------------------------------|----------------------------------|----------------------|-------------|---------------------------|

| Bandwidth          | Low                           | Low/Mid                          | High                 | High        | High                      |

| E2E Latency        | < 1ms                         | <100ms                           | ~10ms                | < 1ms       | 100ms                     |

| Cost               | Low                           | Low                              | High                 | High        | Medium                    |

| Network Technology | CAN/LIN<br>FlexRay/10Base-T1S | CAN/LIN/10Base-T1S<br>100Base-T1 | 1000Base-T1          | 1000Base-T1 | 100Base-T1<br>1000Base-T1 |

17 Huawei Confidential Cyber Defense Center Monitoring & Analysis :0 CycurGUARD . ......

solution of the vehicle infrastructure

#### 2.2 Huawei Automotive In-Vehicle Network Research Group – Research Technologies

T1. High performance in Gatewaying/Tunneling/Routing/Forwarding processing is crucial (E2E latency, jitter, bandwidth, etc.)

a 13 ala 2 ala 2 ala mipi CONTENT PROPERTY ISO (a) (a) lin Break SYNC ID PS SO PH Data PP (CA) Instrument Cluster Rear Lights Loss of Critical Data, Airbag Both Side Failure, ASIL-B Inadvertent Deploy ASIL-A ASIL-D CSI-2 **Rear View Camera** + 14 12 - He 6 He -----**Engine Management** CAN No Valid Sensor Data, o Arbitration Contro CRC Ack EDF IFS Unwanted Acceleration, ----ASIL-B ASIL-C to D **MIPI CSI-2 Packets** Ack EOF IFS PCIe Layer HeadLights **Brake Lights** Both Side Failure, Transaction Laver Packet (TLP) Application Both Side Failure, ASIL-B 0. 119.4 Transaction -----PCI> Start Data Link CONKL Reinte Au EOF 195 **Radar Cruise Control** 4 B 2 Physical ing Inadvertent Braking, Power Braking, ASIL-B .... 802101 Cycle **Electric Power Steering** ( **Active Suspension** Vision ADAS Suspension Oscillates, Incorrect Sensor Feedback, Self-steering, ASIL-B to C ASIL-B ASIL-D Source: Synopsys ther with FuSa, deployed in the Zonal Gateway Controller is key in order to achieve a holistic security T4. The deployment of Application Layer functionality in zonal GW controllers, on top of the IVN infrastru frastructure right level of reliability, performance and cost-effectiveness Intrusion Detection and Prevention Applications Powertrain/Chassis Body/Comfort Cockpit/Infotainment ADAS/AD Bandwidth Cyber Defense Center Low Low/Mid High High security interfaces Monitoring & Analysis E2E Latency < 1ms <100ms ~10ms < 1ms 100ms Cost Low High High Medium Low 2 Security gateway CAN/LIN CAN/LIN/10Base-T1S 100Base-T1 1000Base-T1 1000Base-T1 Secure network Network Technology FlexRay/10Base-T1S 100Base-T1 1000Base-T1 :0 CycurGUARD Secure processing Internal processors, ECUs, edge storage . operating systems, file systems, etc. ...... 18 Huawei Confidential

T2. Functional Safety is getting more and more attention in the ACES vehicle of tomorrow

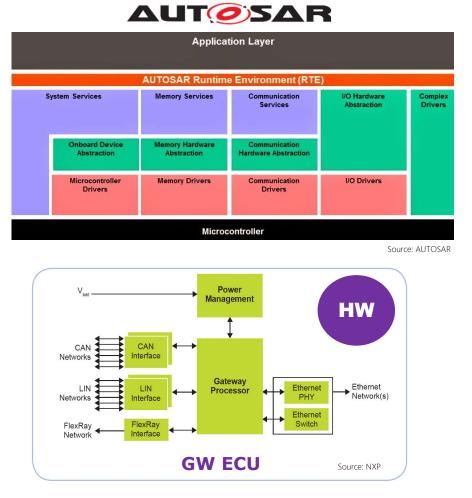

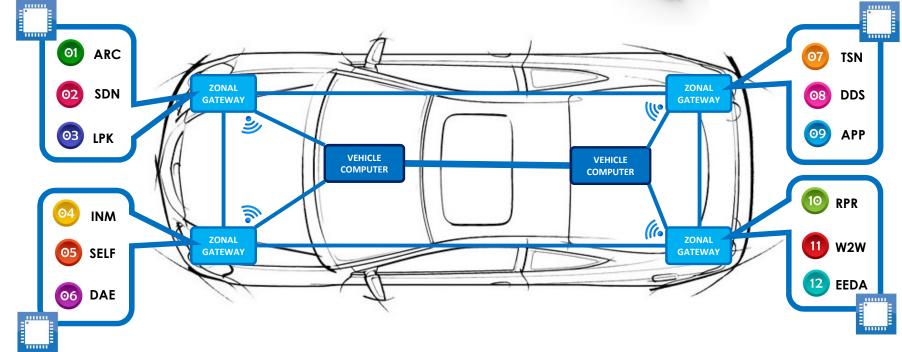

## 2.3 Zonal Gateway Controller – Conceptualization & Requeriments

All in all, the **Zonal Gateway Controller** is probably one of the <u>most complex networking devices ever</u>, at least in terms of mixing heterogeneous application functionality and networking technologies

Zonal GW Controller = Application (Cross-Domain) Functions + Networking & Power Distribution + Safety & Security

We HUAWEI

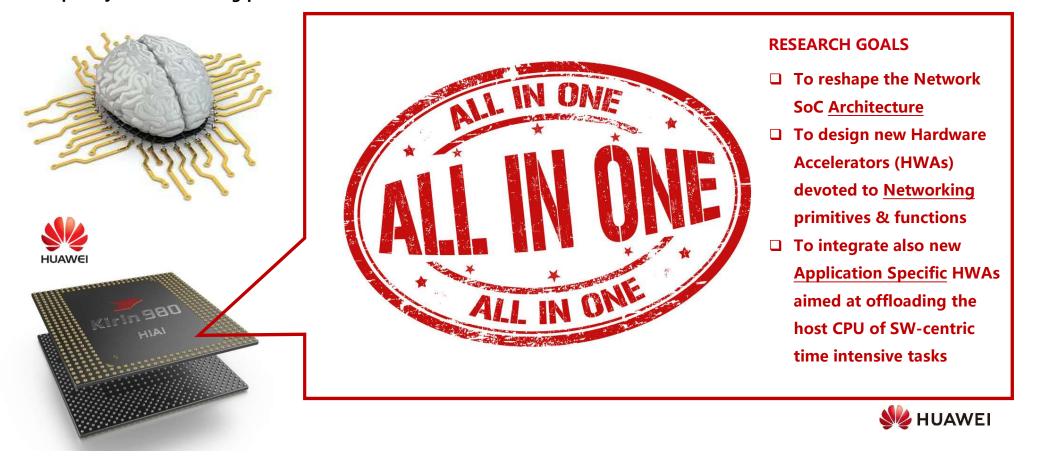

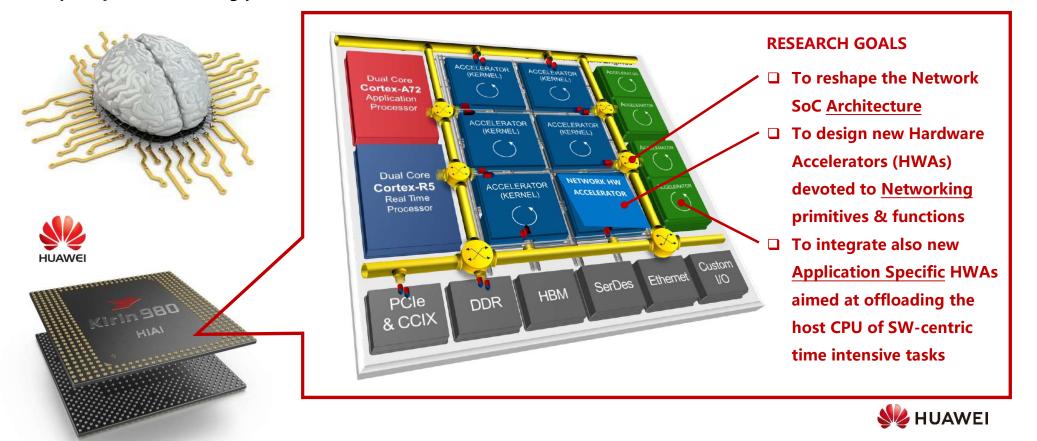

### 2.4 Our HW-centric Solution: Elastic Gateway SoC (eGW)

CHALLENGE: In search of the right HW/SW/NW codesign in order to deliver a well balanced high performing, safe and secure Zonal Gateway Controller/SoC product architecture able to solve the current engineering pain points and meet all the demanded requirements

火 HUAWEI

#### 2.4 Our HW-centric Solution: Elastic Gateway SoC (eGW)

HOW? Our target is to design and develop a new SoC architecture provided with innovative hardware accelerators (i.e. standardizable peripherals or coprocessors) to accomplish the whole set of cyber physical system (i.e. SDV) requirements, while minimizing complexity and maximizing performance at affordable cost

### 2.4 Our HW-centric Solution: Elastic Gateway SoC (eGW)

HOW? Our target is to design and develop a new SoC architecture provided with innovative hardware accelerators (i.e. standardizable peripherals or coprocessors) to accomplish the whole set of cyber physical system (i.e. SDV) requirements, while minimizing complexity and maximizing performance at affordable cost

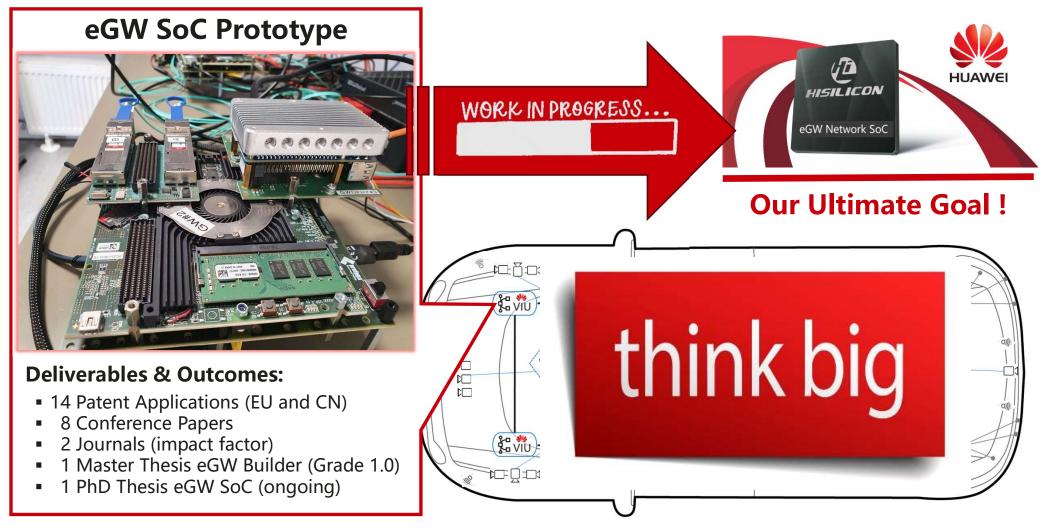

### 2.5 eGW SoC Prototyping

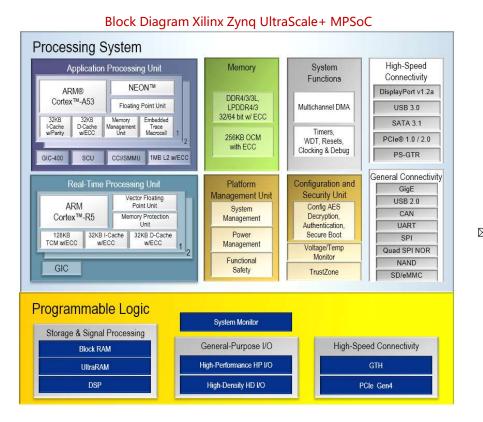

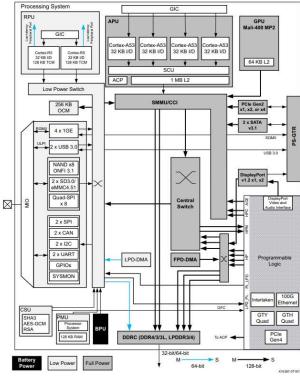

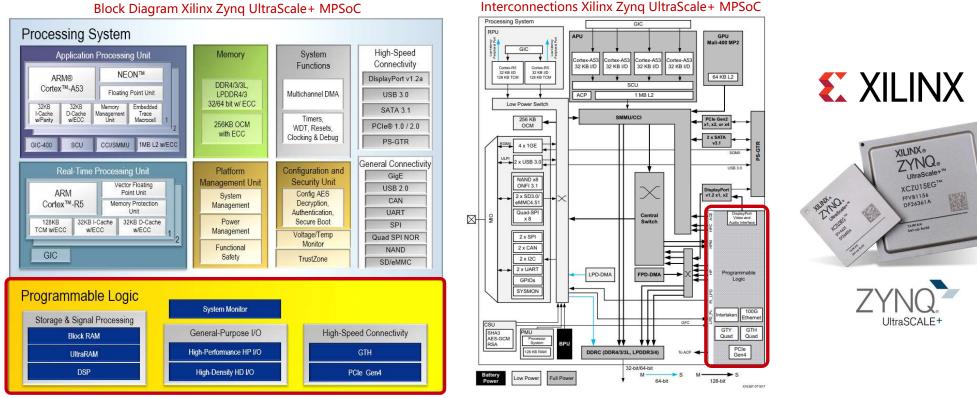

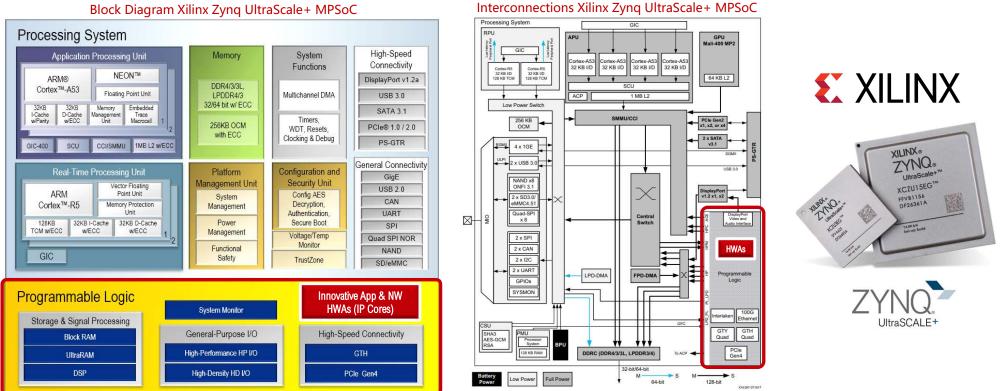

#### HOW? Xilinx Zynq UltraScale+ MPSoC is the prototyping platform chosen to deploy our HW-centric eGW SoC Concept

#### Interconnections Xilinx Zyng UltraScale+ MPSoC

# **E** XILINX

### 2.5 eGW SoC Prototyping

#### HOW? Xilinx Zyng UltraScale+ MPSoC is the prototyping platform chosen to deploy our HW-centric eGW SoC Concept

24 Huawei Confidential

#### Interconnections Xilinx Zyng UltraScale+ MPSoC

**W**HUAWEI

### 2.5 eGW SoC Prototyping

#### HOW? Xilinx Zyng UltraScale+ MPSoC is the prototyping platform chosen to deploy our HW-centric eGW SoC Concept

Block Diagram Xilinx Zyng UltraScale+ MPSoC

# Contents

# **1. [WHY] Automotive Electronic Industry**

- The Innovation Race

- Pain Points & Challenges

## 2. [HOW] IVN, Zonal GW Controller & Networking Chipset

- Huawei Automotive IVN Research Group

- Zonal Gateway Controller

- Network SoC Prototyping

## 3. [WHAT] Elastic Gateway SoC (eGW) Concept

- Related Art on HW/SW Codesign in Automotive

- The 12 HW Innovations on NW & APP Processing of eGW SoC

#### 3.2 The 12 HW-centric Innovations for Networking & App Processing deployed in eGW SoC

The **Game Changer** is a new <u>SoC Architecture</u> carefully crafted for networking and accelerating the execution of applications in Zonal GWs aimed at reducing SW complexity and offloading the CPU. The exploration of innovative <u>HW Accelerators (HWAs</u>) is in the **DNA of our Research**. Up to <u>12 HW innovations</u> have been developed to be integrated in NG Zonal GW SoCs.

34

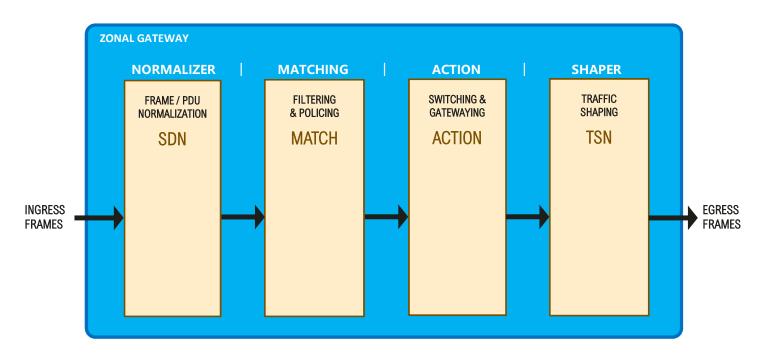

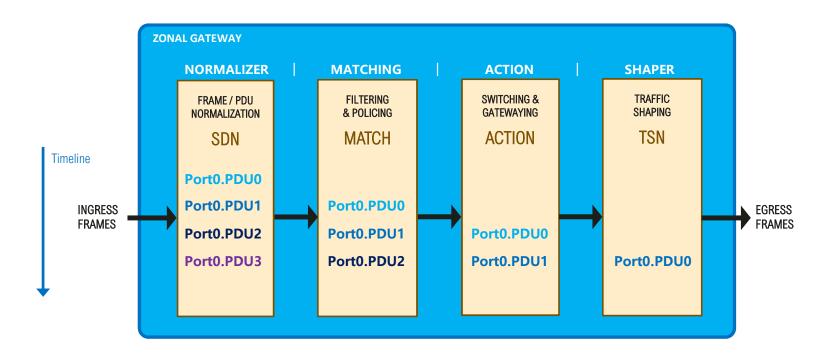

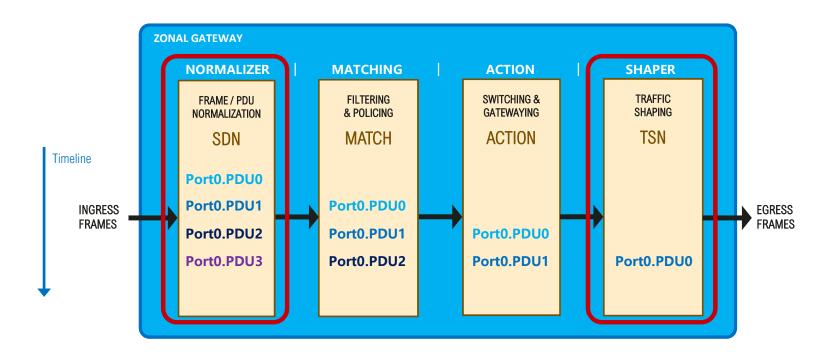

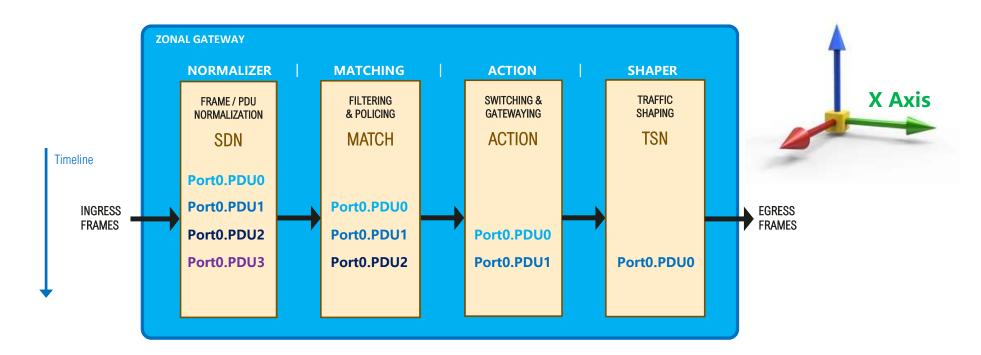

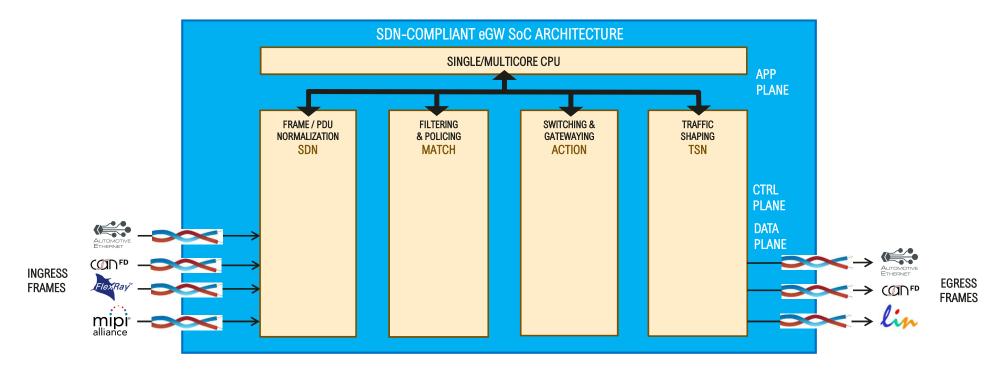

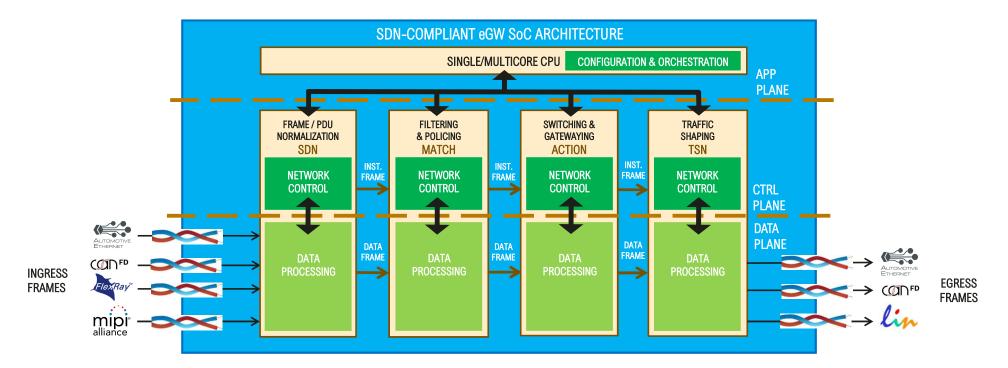

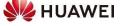

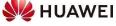

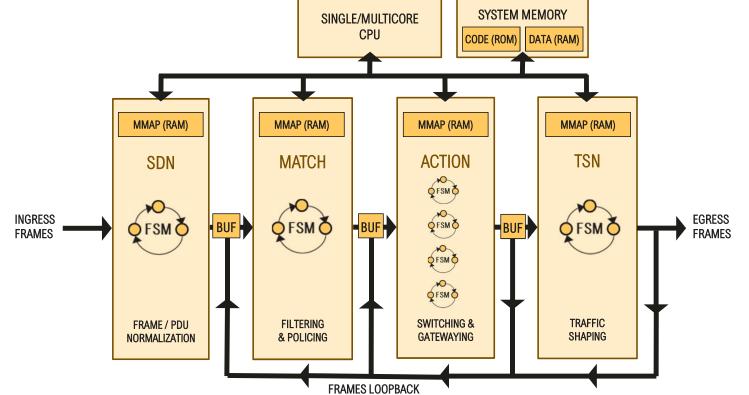

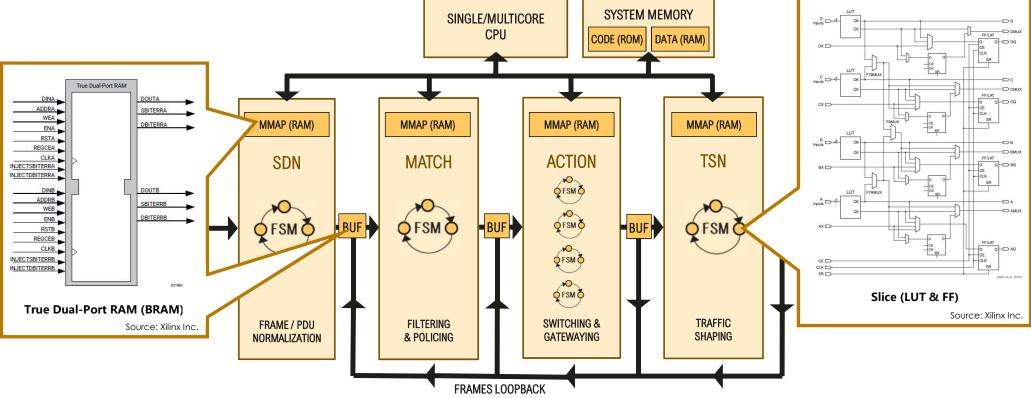

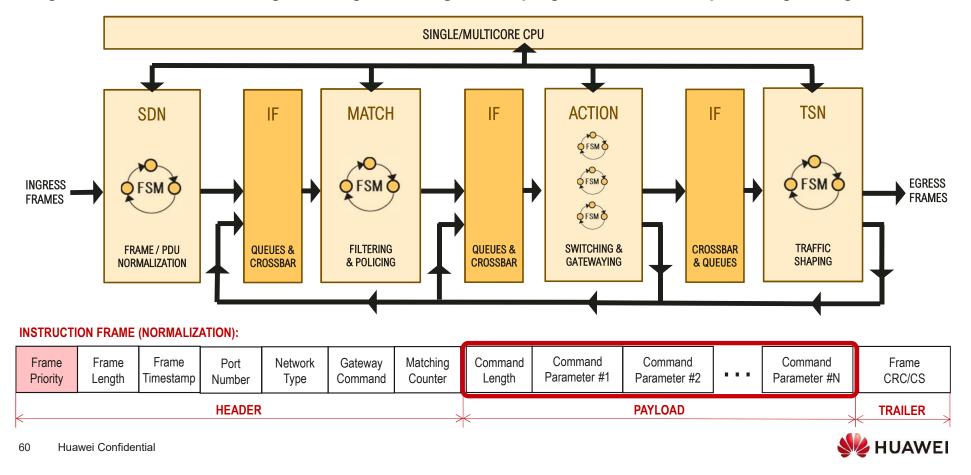

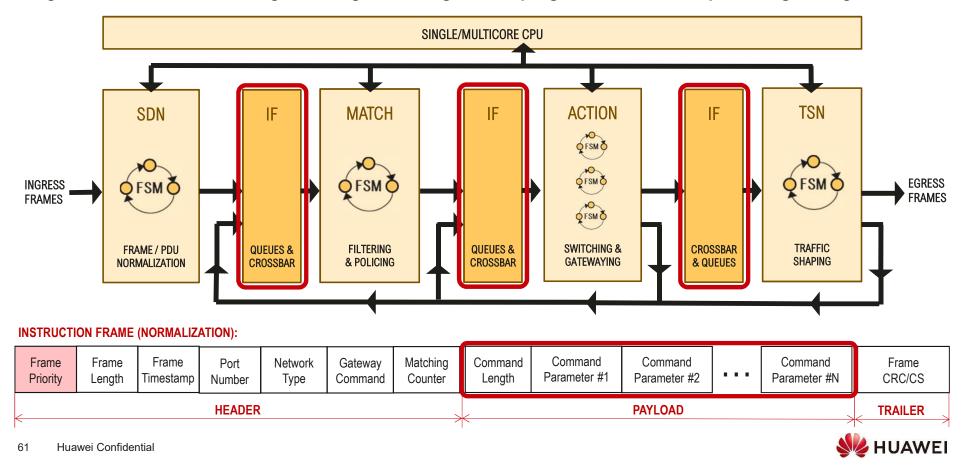

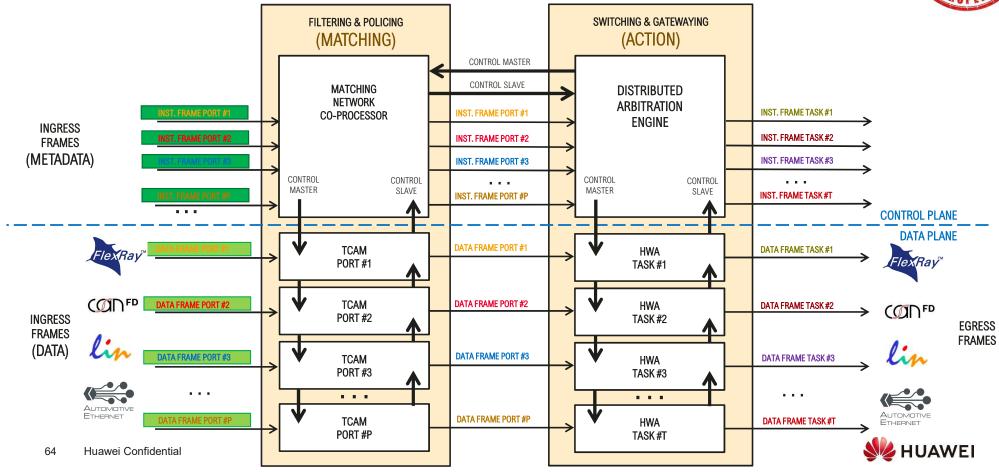

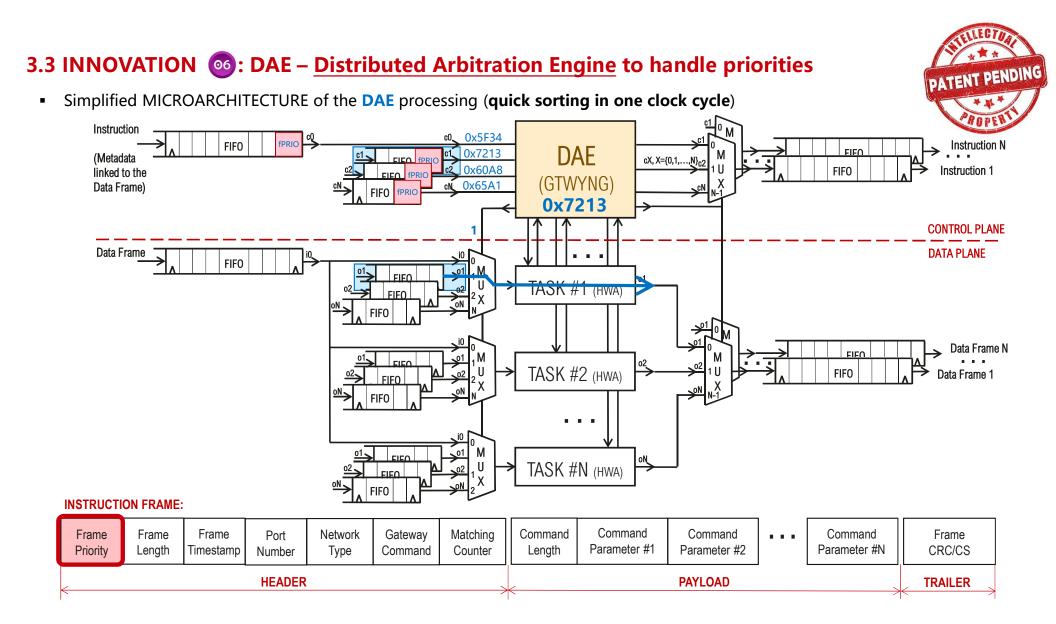

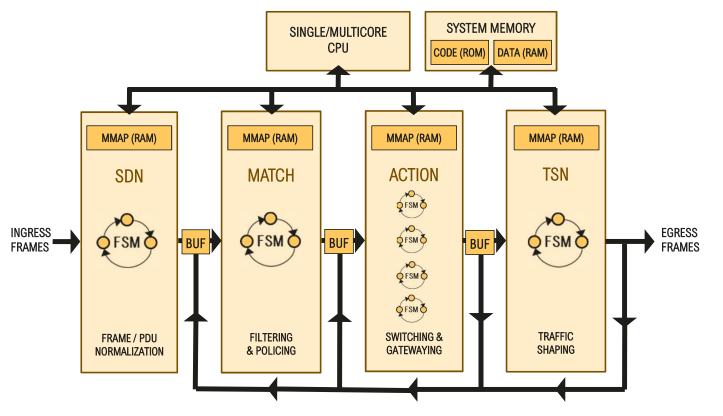

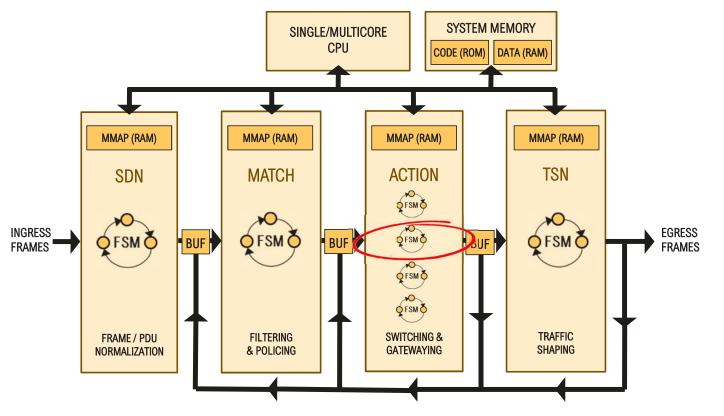

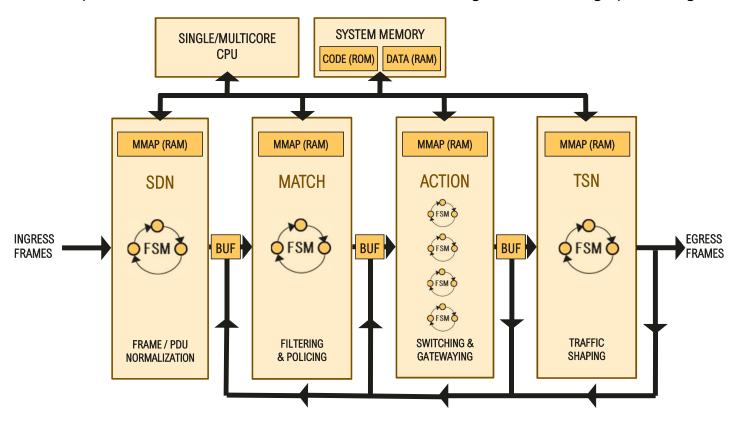

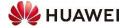

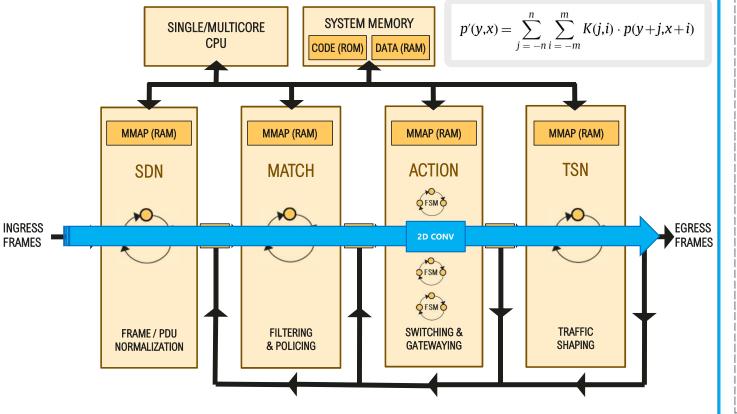

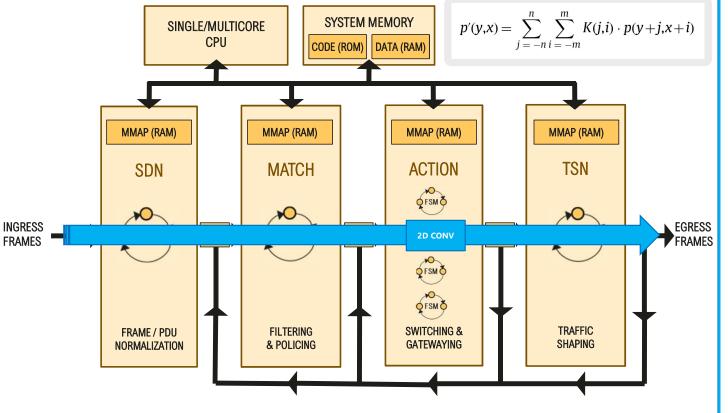

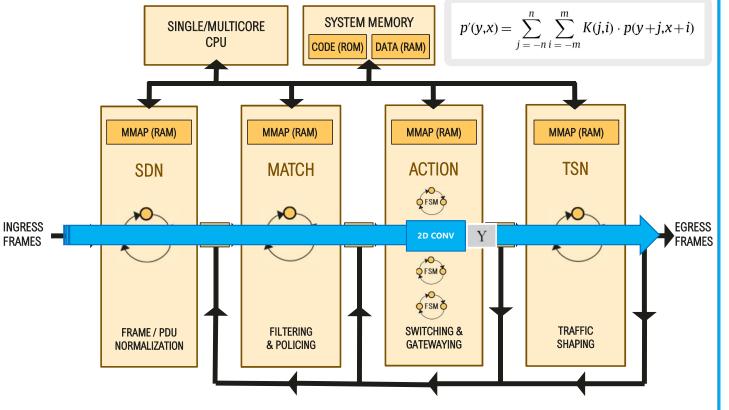

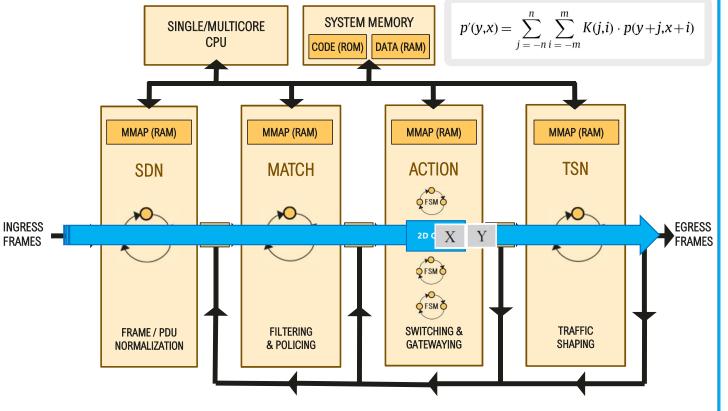

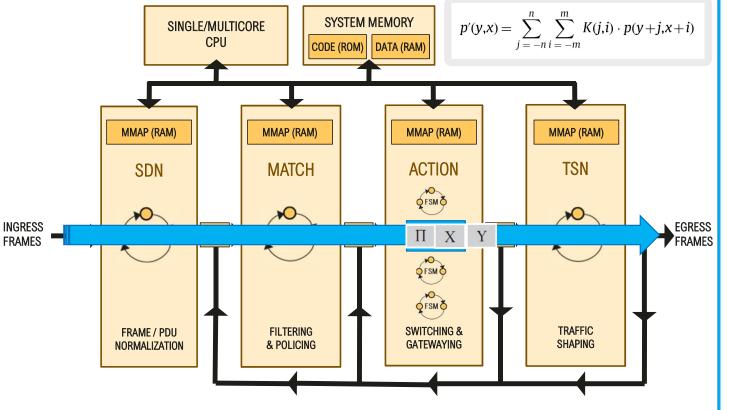

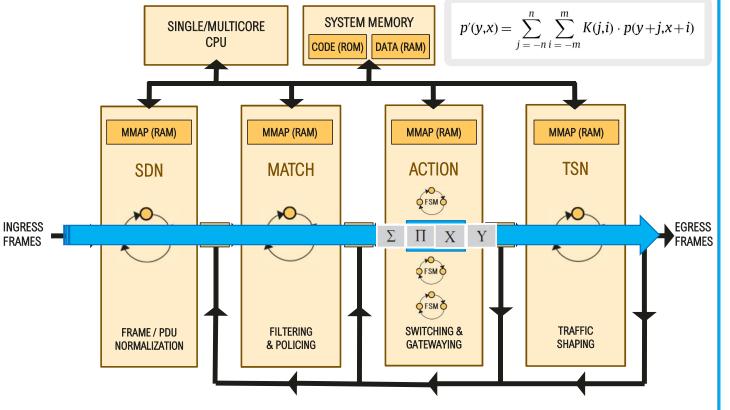

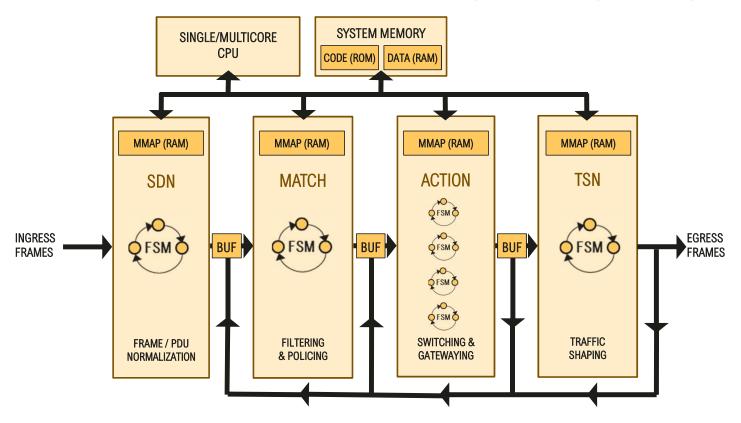

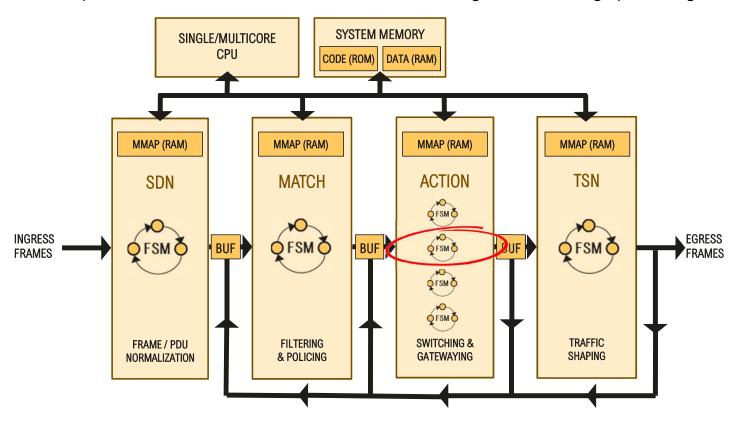

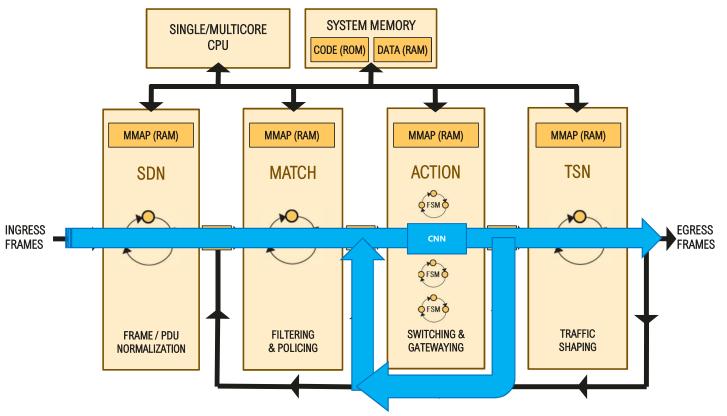

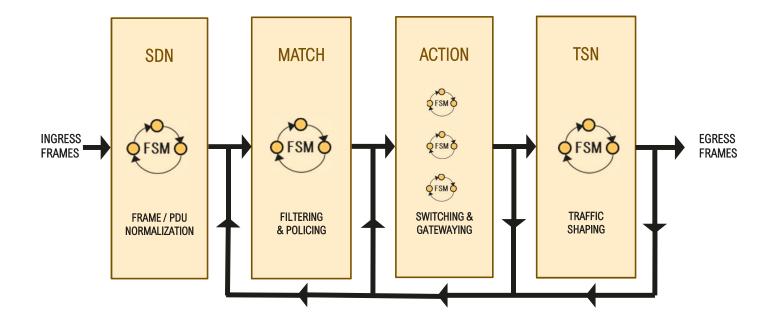

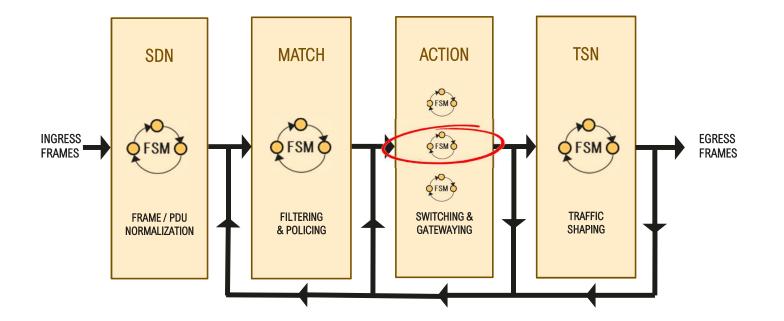

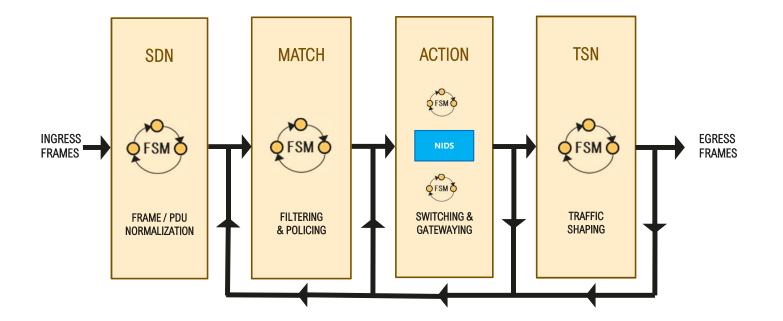

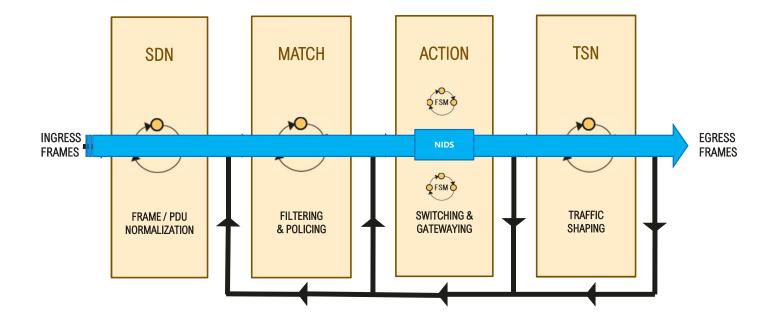

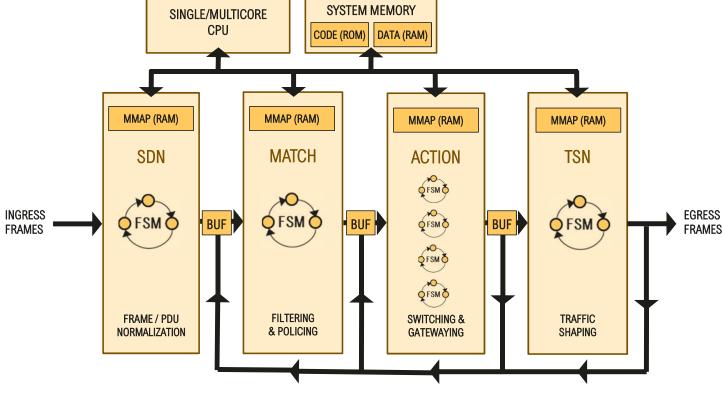

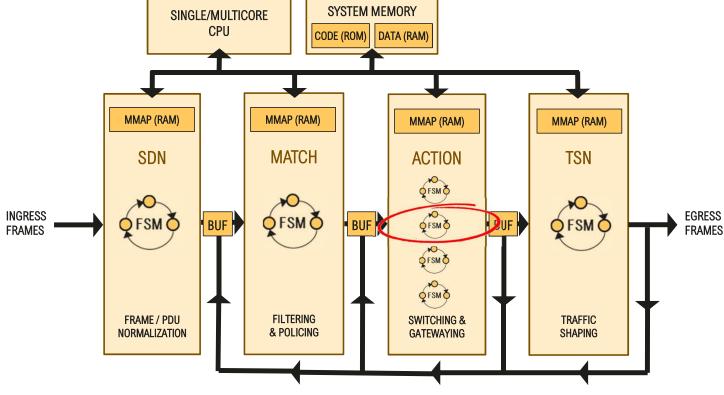

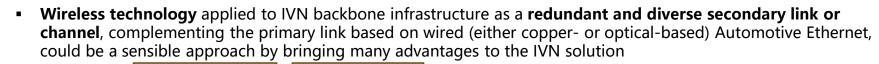

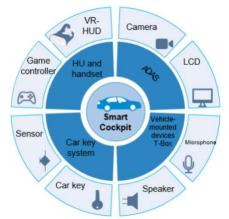

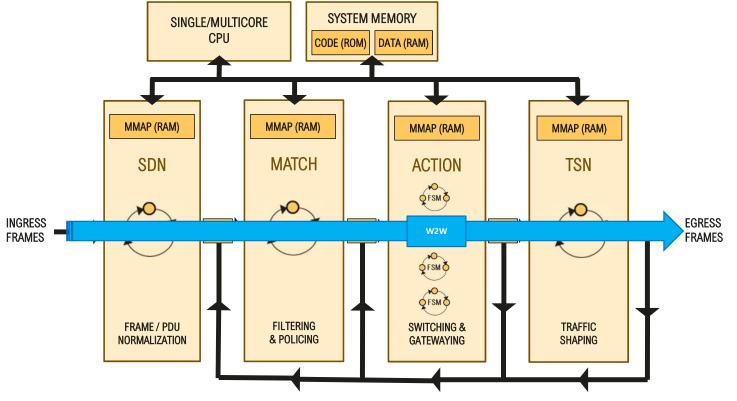

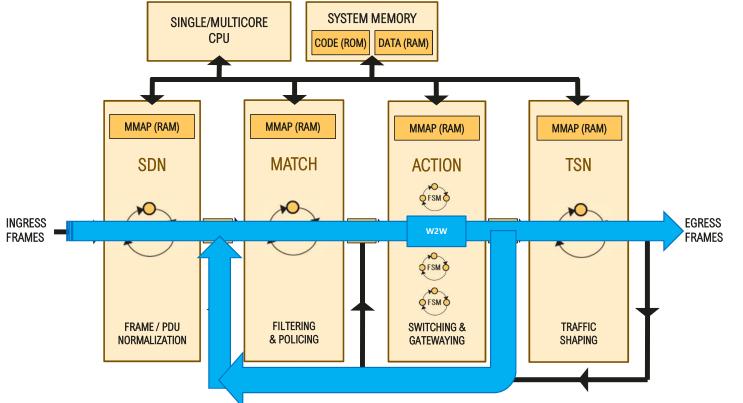

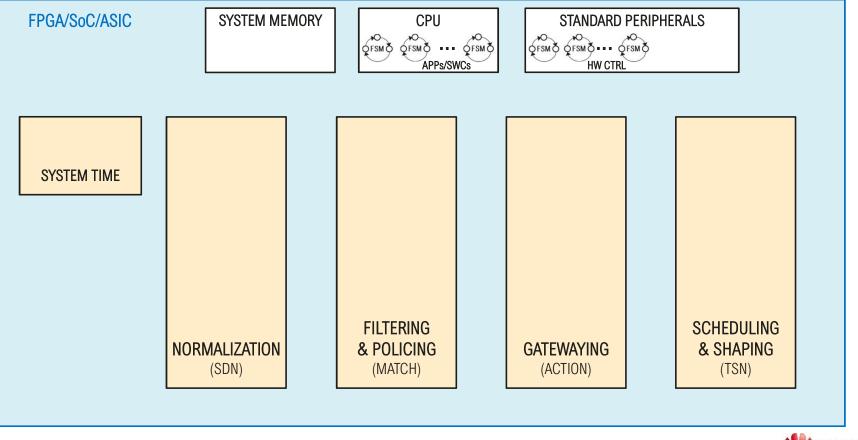

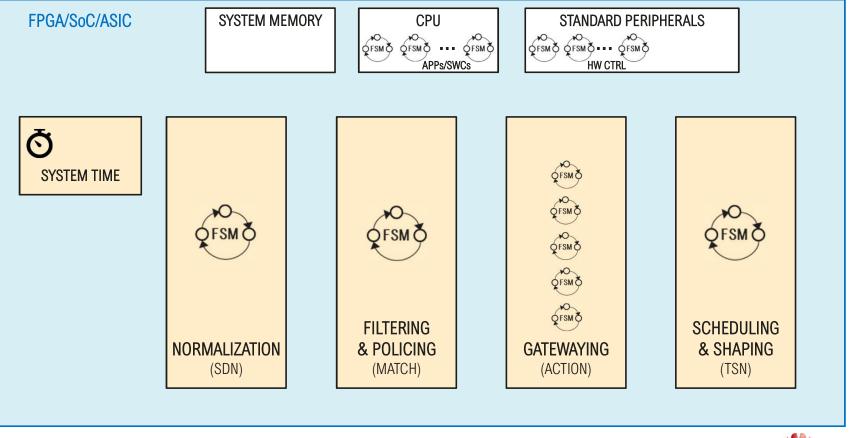

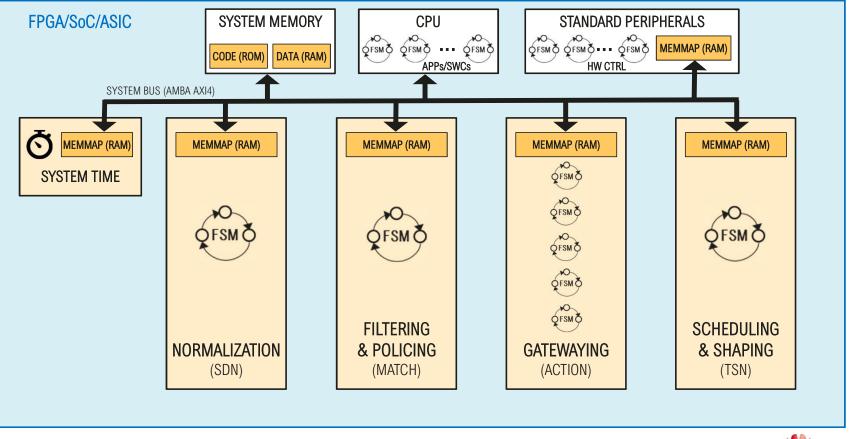

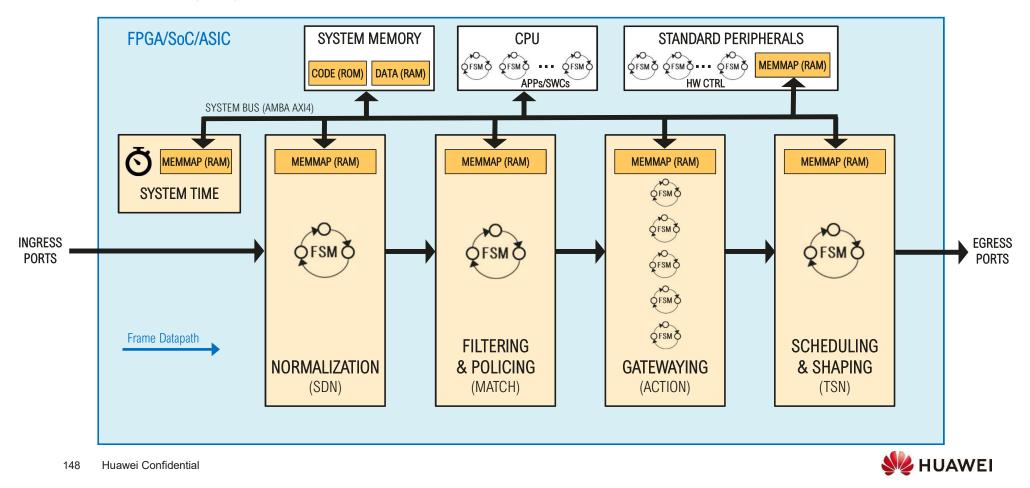

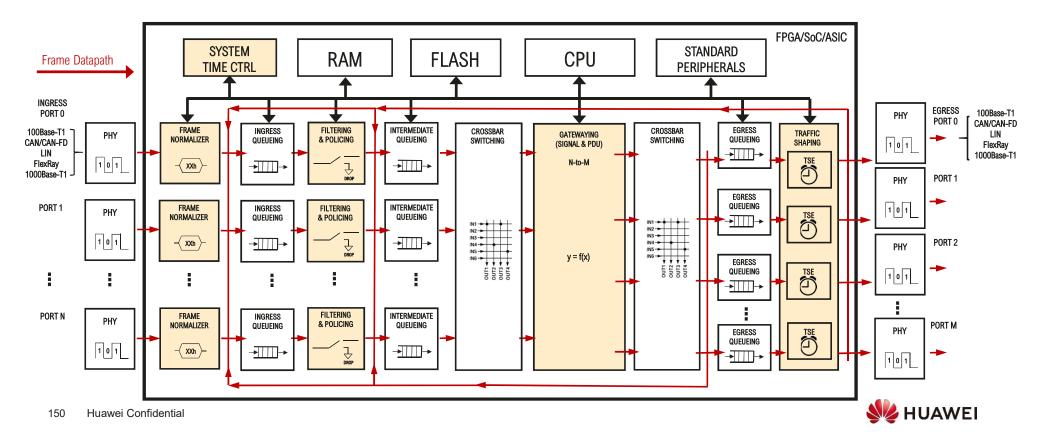

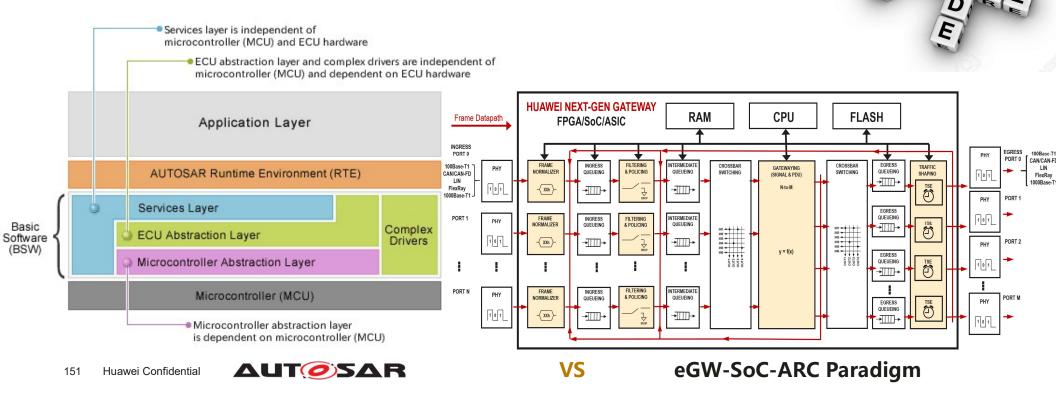

## 3.3 INNOVATION (1): ARC – Our Elastic Network SoC <u>Reference Architecture</u> (eGW)

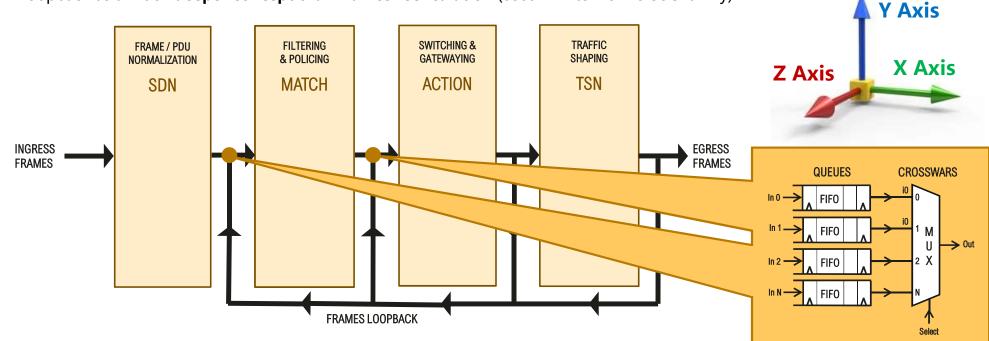

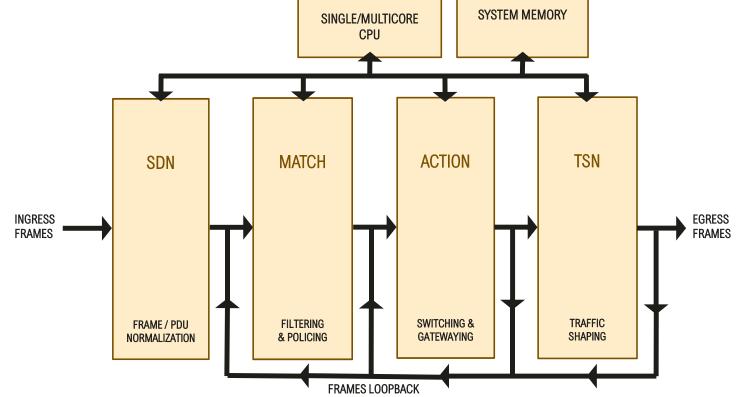

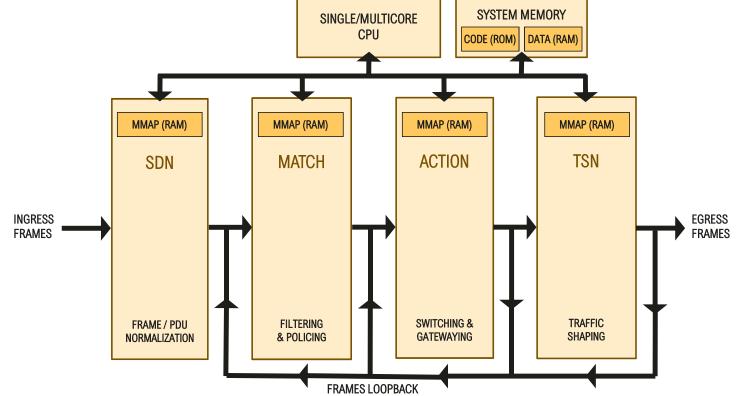

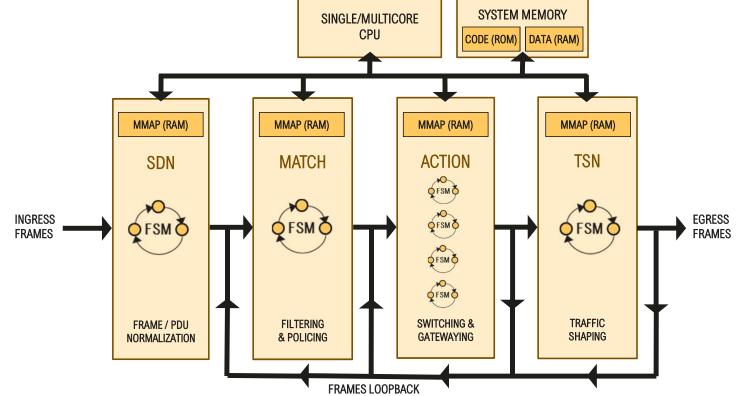

- Modeling of a four-stage pseudo-pipeline as regular data path pioneering a HW-centric inline ingress-to-egress processing through HWAs by exploiting parallelism

- Innovative PDU normalization (SDN parsing) as first stage and traffic scheduling/shaping as last stage (ns/µs time handling) in between the typical frame processing stages of Matching & Action (M&A)

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

## 3.3 INNOVATION (1): ARC – Our Elastic Network SoC <u>Reference Architecture</u> (eGW)

- Modeling of a four-stage pseudo-pipeline as regular data path pioneering a HW-centric inline ingress-to-egress processing through HWAs by exploiting parallelism

- Innovative PDU normalization (SDN parsing) as first stage and traffic scheduling/shaping as last stage (ns/µs time handling) in between the typical frame processing stages of Matching & Action (M&A)

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

## 3.3 INNOVATION (1): ARC – Our Elastic Network SoC <u>Reference Architecture</u> (eGW)

- Modeling of a four-stage pseudo-pipeline as regular data path pioneering a HW-centric inline ingress-to-egress processing through HWAs by exploiting parallelism

- Innovative PDU normalization (SDN parsing) as first stage and traffic scheduling/shaping as last stage (ns/µs time handling) in between the typical frame processing stages of Matching & Action (M&A)

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

🔌 HUAWEI

## 3.3 INNOVATION (1): ARC – Our Elastic Network SoC <u>Reference Architecture</u> (eGW)

- Modeling of a four-stage pseudo-pipeline as regular data path pioneering a HW-centric inline ingress-to-egress processing through HWAs by exploiting parallelism

- Innovative PDU normalization (SDN parsing) as first stage and traffic scheduling/shaping as last stage (ns/µs time handling) in between the typical frame processing stages of Matching & Action (M&A)

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

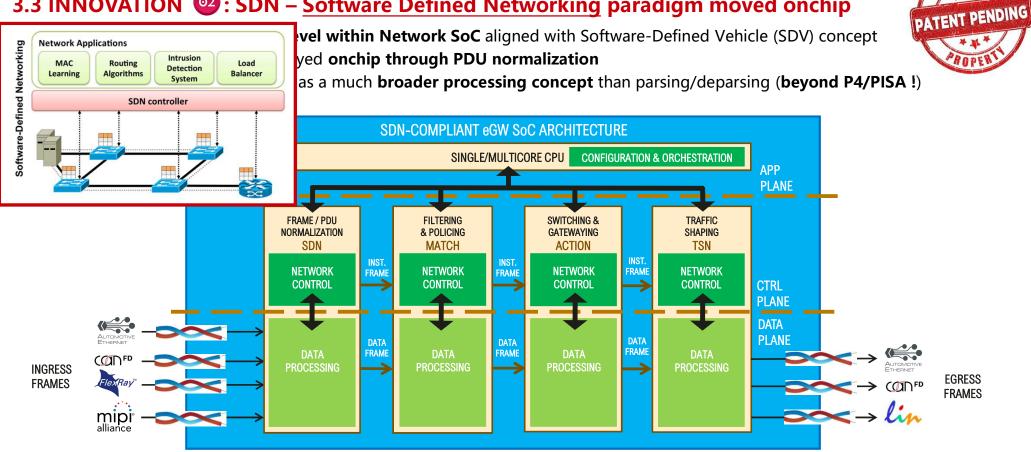

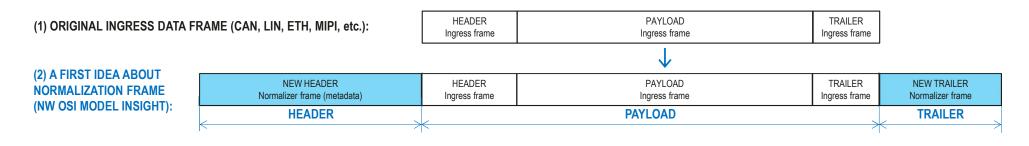

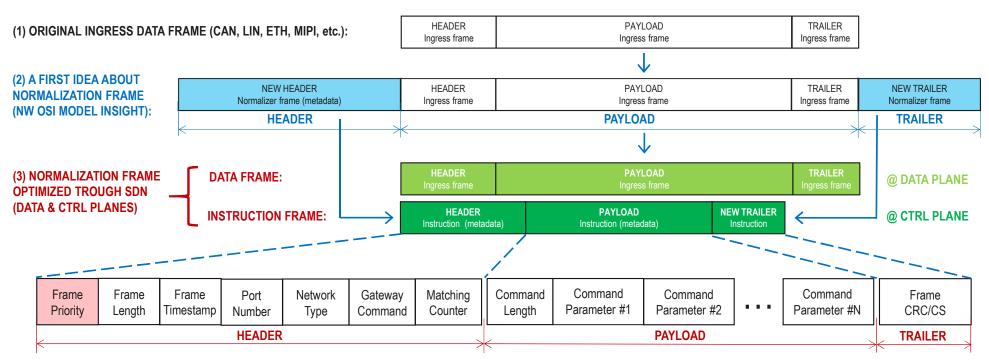

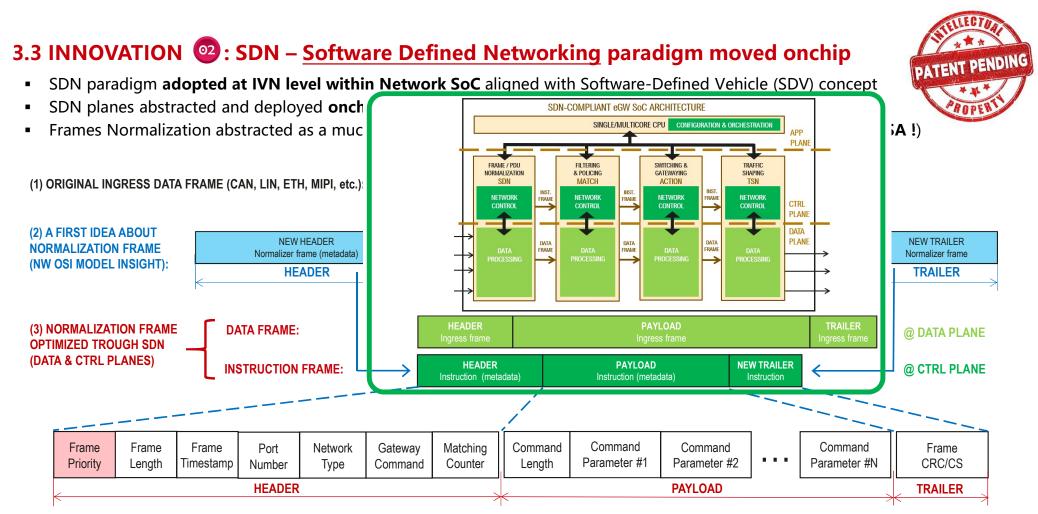

- SDN paradigm **adopted at IVN level within Network SoC** aligned with Software-Defined Vehicle (SDV) concept

- SDN planes abstracted and deployed onchip through PDU normalization

- Frames Normalization abstracted as a much broader processing concept than parsing/deparsing (beyond P4/PISA !)

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

- SDN paradigm **adopted at IVN level within Network SoC** aligned with Software-Defined Vehicle (SDV) concept

- SDN planes abstracted and deployed onchip through PDU normalization

- Frames Normalization abstracted as a much broader processing concept than parsing/deparsing (beyond P4/PISA !)

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

Rationale: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in heterogeneous PDUs in order to make them protocol agnostic.

- SDN paradigm adopted at IVN level within Network SoC aligned with Software-Defined Vehicle (SDV) concept

- SDN planes abstracted and deployed onchip through PDU normalization

- Frames Normalization abstracted as a much broader processing concept than parsing/deparsing (beyond P4/PISA !)

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

42 Huawei Confidential

PATENT PENDING

- SDN paradigm **adopted at IVN level within Network SoC** aligned with Software-Defined Vehicle (SDV) concept

- SDN planes abstracted and deployed onchip through PDU normalization

- Frames Normalization abstracted as a much broader processing concept than parsing/deparsing (beyond P4/PISA !)

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

- SDN paradigm adopted at IVN level within Network SoC aligned with Software-Defined Vehicle (SDV) concept

- SDN planes abstracted and deployed onchip through PDU normalization

- Frames Normalization abstracted as a much broader processing concept than parsing/deparsing (beyond P4/PISA !)

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

**<u>Rationale</u>**: Effective decoupling of data (data forwarding from data plane) and metadata (network orchestration from control plane) in **heterogeneous PDUs** in order to make them **protocol agnostic**.

45 Huawei Confidential

#### 💐 HUAWEI

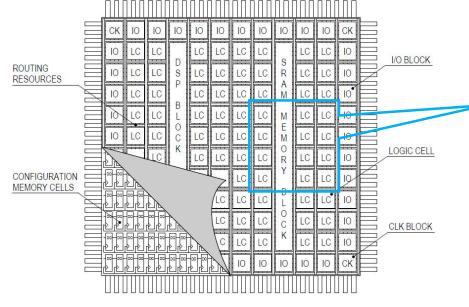

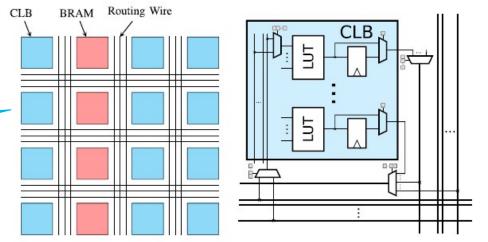

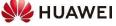

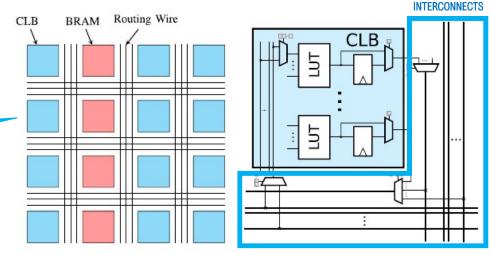

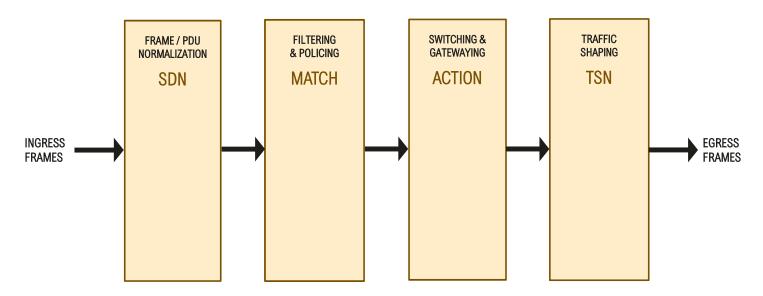

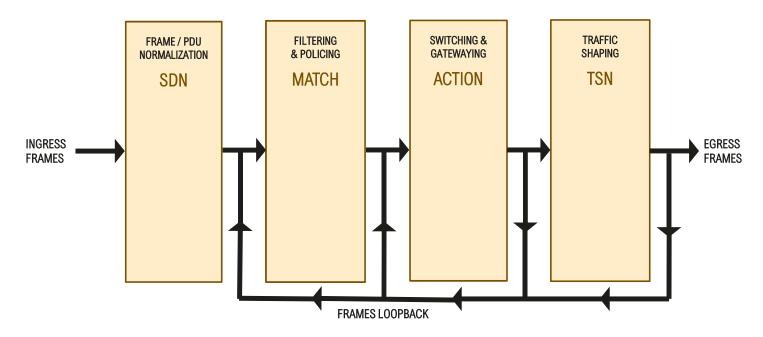

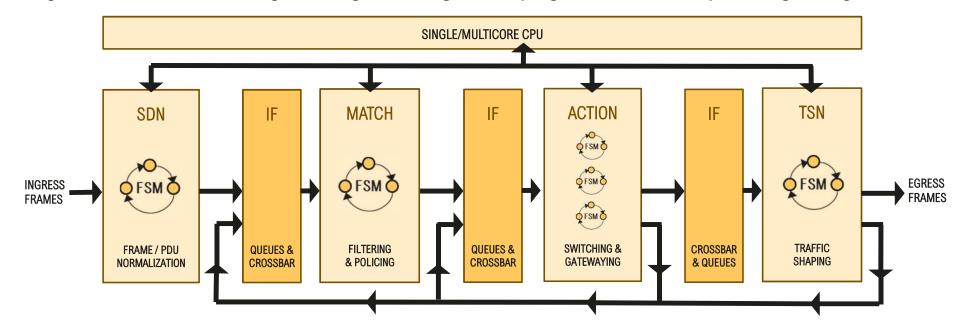

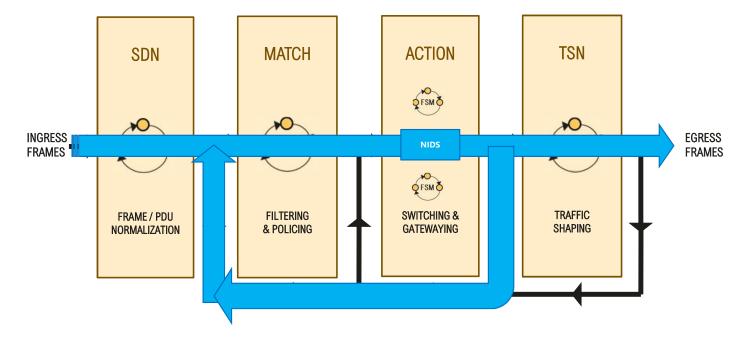

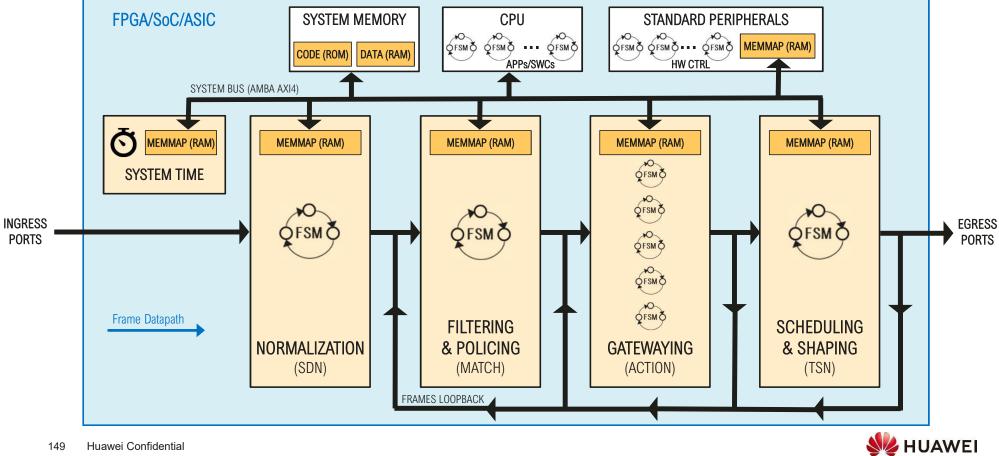

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66): DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

|                               | П |              |          | 100         |    |    |    | 100 |                                      |    |    |    |    |           |

|-------------------------------|---|--------------|----------|-------------|----|----|----|-----|--------------------------------------|----|----|----|----|-----------|

|                               |   | к 10         | 10       | 10          | 10 | 10 | 10 | 10  | 10                                   | 10 | 10 | СК | E  |           |

| ROUTING<br>RESOURCES          |   |              | LC<br>LC | D<br>S<br>P | LC | LC | LC | LC  | S<br>R<br>A<br>M<br>E                | LC | LC | 10 |    | I/O BLOCK |

|                               |   |              |          |             |    | LC | LC | LC  |                                      | LC | LC | 10 | R  |           |

|                               | X |              | LC       | B           | LC | LC | LC | LC  |                                      | LC | LC | 10 |    |           |

|                               |   | 2 IC         | LC       | L           | LC | LC | LC | LC  |                                      | LC | LC | 10 |    |           |

|                               |   | 0.0          | LC       | O<br>C<br>K | LC | LC | LC | LC  | M                                    | LC | LC | 10 |    |           |

| CONFIGURATION<br>MEMORY CELLS |   |              | LC       | r.          | LC | LC |    | LC  | O<br>R<br>Y<br>B<br>L<br>O<br>C<br>K | LC | LC | 10 | EX |           |

|                               |   |              |          |             | -  |    | LC | LC  |                                      | LC | LC | 10 |    |           |

|                               |   |              |          |             |    | LC | LC | LC  |                                      | LC | LC | 10 |    |           |

|                               |   |              |          |             |    | LC | LC |     |                                      | LC | LC | 10 |    | CLK BLOCK |

|                               |   |              |          |             |    | C  | LC | LC  |                                      | LC | LC | 10 | R  |           |

|                               |   | ┉┉┉<br>ํ๛๛๛๛ |          |             |    |    | 10 | 10  | 10                                   | 10 | 10 | СК |    |           |

|                               | Ι |              |          |             |    |    |    |     |                                      |    |    |    |    |           |

Generic SRAM-based FPGA Architecture

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66: DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

Generic SRAM-based FPGA Architecture

**Figure.** (Left) An FPGA consisting of logic cells (LC) / configurable logic blocks (CLB) and Block RAM (BRAM), along with programmable routing to interconnect them. (Right) Each CLB contains Look Up Tables (LUT) and flip-flops (FF). Routing Muxes are configured to interconnect elements with each block or interblock routing wires.

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66: DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

Generic SRAM-based FPGA Architecture

**Figure.** (Left) An FPGA consisting of logic cells (LC) / configurable logic blocks (CLB) and Block RAM (BRAM), along with programmable routing to interconnect them. (Right) Each CLB contains Look Up Tables (LUT) and flip-flops (FF). Routing Muxes are configured to interconnect elements with each block or interblock routing wires.

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

48 Huawei Confidential

LOOPBACK CAPABLE

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66: DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

<u>Rationale</u>: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

HUAWEI

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66): DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

HUAWEI

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 66: DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

51 Huawei Confidential

HUAWEI

- Loopback brings flexibility (insight from FPGA-based combinational/sequential digital circuits based on LUT+FF+Interconnect)

- Interconnects of network processing stages through queues and crossbars

- Still effective in latency when combined with prioritization and arbitration strategy (refer to innovation 06): DAE)

- Loopback as a much deeper concept than frames recirculation (used in Intel Tofino SoC family)

**<u>Rationale</u>**: Elastic processing path for frames, **back and forth**, not only fast forward but also fast feedback (with prioritization and arbitration strategy) and well balanced with other KPIs (high-performance, latency, jitter, bandwidth, throughput)

52 Huawei Confidential

💐 HUAWEI

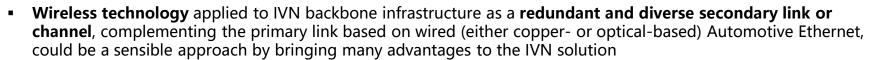

#### 3.3 INNOVATION 🥶 : INM – <u>In-memory</u> local processing is the real enabler for offloading CPUs

Our HWAs synthesized through onchip centralized Block RAM (true dual-port RAM, FIFO) and distributed local RAM (LUTs, FFs) optimize inline and parallel processing

**<u>Rationale</u>**: Overall, much more **onchip memory** is required in a Network SoC. Onchip local memory is the best option and it pays off because data movement is expensive in terms of **energy consumption**! That is, external DDRx memory to be skipped if possible.

🜽 HUAWEI

### 3.3 INNOVATION 🥶 : INM – <u>In-memory</u> local processing is the real enabler for offloading CPUs

Our HWAs synthesized through onchip centralized Block RAM (true dual-port RAM, FIFO) and distributed local RAM (LUTs, FFs) optimize inline and parallel processing

**<u>Rationale</u>**: Overall, much more **onchip memory** is required in a Network SoC. Onchip local memory is the best option and it pays off because data movement is expensive in terms of **energy consumption**! That is, external DDRx memory to be skipped if possible.

🜽 HUAWEI

### 3.3 INNOVATION 4 : INM – In-memory local processing is the real enabler for offloading CPUs

Our HWAs synthesized through onchip centralized Block RAM (true dual-port RAM, FIFO) and distributed local RAM (LUTs, FFs) optimize inline and parallel processing

Rationale: Overall, much more onchip memory is required in a Network SoC. Onchip local memory is the best option and it pays off because data movement is expensive in terms of energy consumption! That is, external DDRx memory to be skipped if possible. HUAWEI

### 3.3 INNOVATION 4 : INM – <u>In-memory</u> local processing is the real enabler for offloading CPUs

Our HWAs synthesized through onchip centralized Block RAM (true dual-port RAM, FIFO) and distributed local RAM (LUTs, FFs) optimize inline and parallel processing

Rationale: Overall, much more onchip memory is required in a Network SoC. Onchip local memory is the best option and it pays off because data movement is expensive in terms of energy consumption! That is, external DDRx memory to be skipped if possible. HUAWEI

### 3.3 INNOVATION 🥶 : INM – <u>In-memory</u> local processing is the real enabler for offloading CPUs

Our HWAs synthesized through onchip centralized Block RAM (true dual-port RAM, FIFO) and distributed local RAM (LUTs, FFs) optimize inline and parallel processing

**<u>Rationale</u>**: Overall, much more **onchip memory** is required in a Network SoC. Onchip local memory is the best option and it pays off because data movement is expensive in terms of **energy consumption**! That is, external DDRx memory to be skipped if possible.

57 Huawei Confidential

💐 HUAWEI

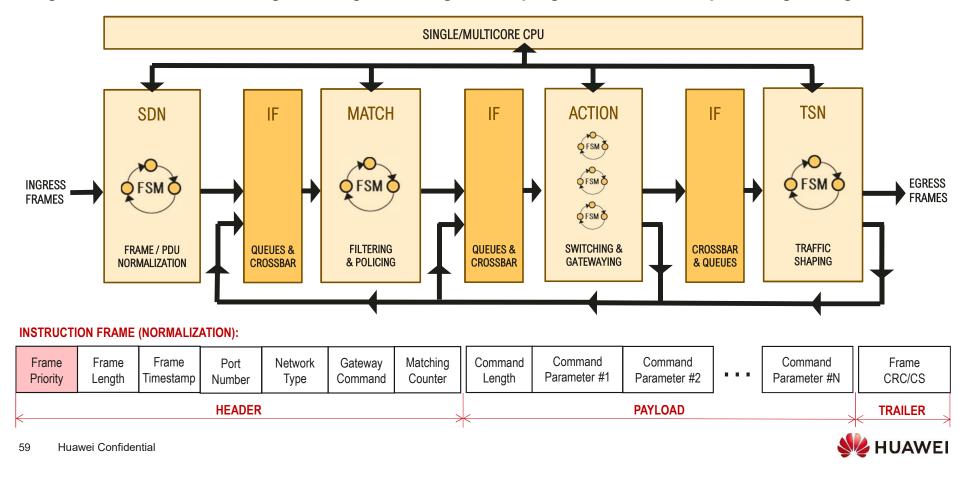

Avoidance of buffering intermediate computation data (e.g. counters & flags) inside HWAs by inserting queues between stages and using the instruction itself as storage, reaching thus the right decoupling between data and processing (scaling solution)

Avoidance of buffering intermediate computation data (e.g. counters & flags) inside HWAs by inserting queues between stages and using the instruction itself as storage, reaching thus the right decoupling between data and processing (scaling solution)

Avoidance of buffering intermediate computation data (e.g. counters & flags) inside HWAs by inserting queues between stages and using the instruction itself as storage, reaching thus the right decoupling between data and processing (scaling solution)

Avoidance of buffering intermediate computation data (e.g. counters & flags) inside HWAs by inserting queues between stages and using the instruction itself as storage, reaching thus the right decoupling between data and processing (scaling solution)

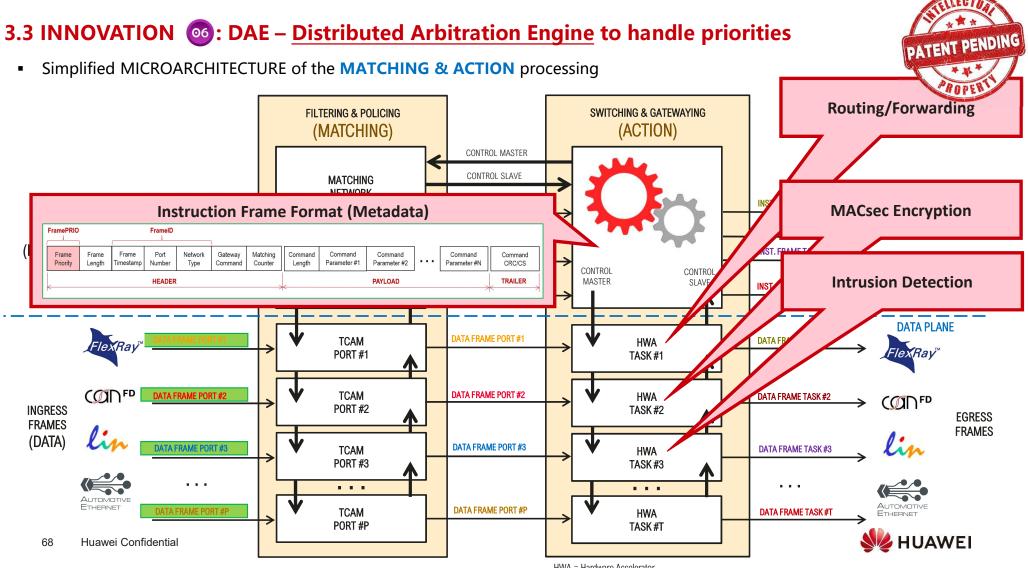

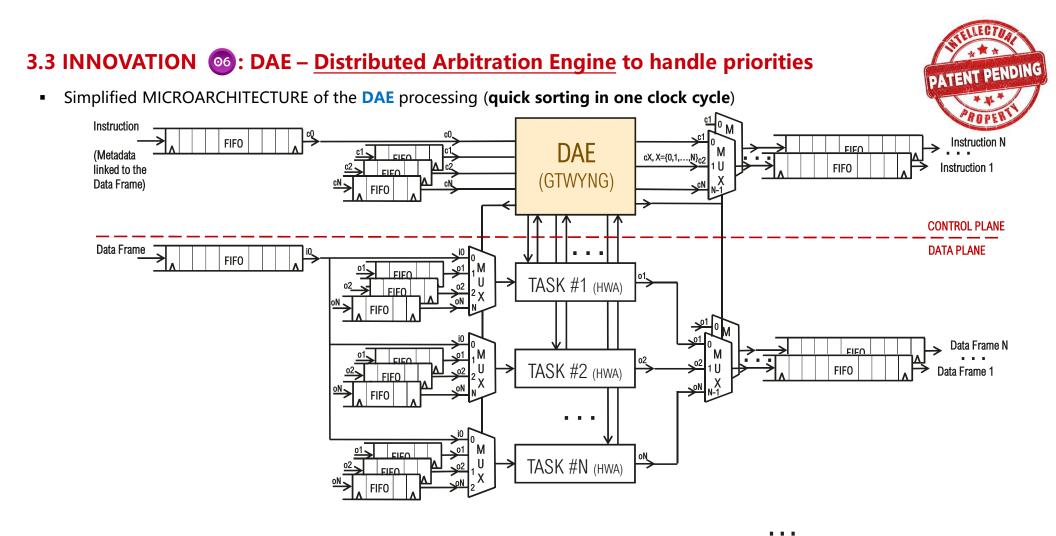

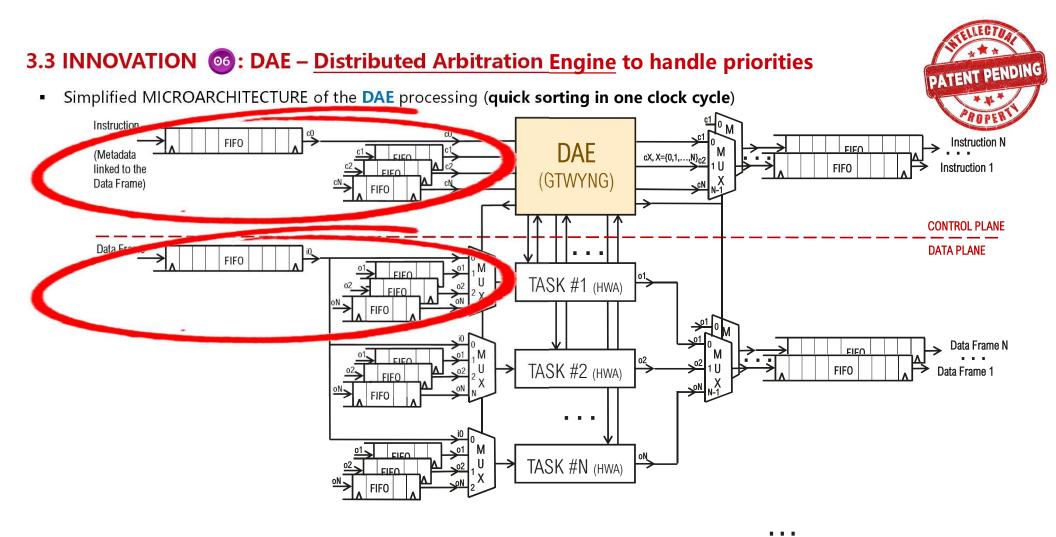

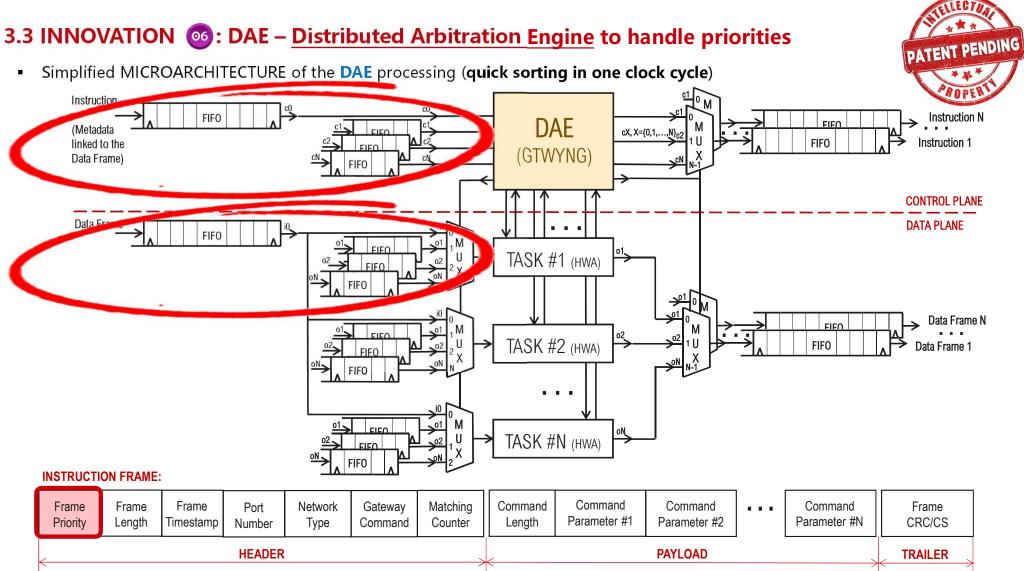

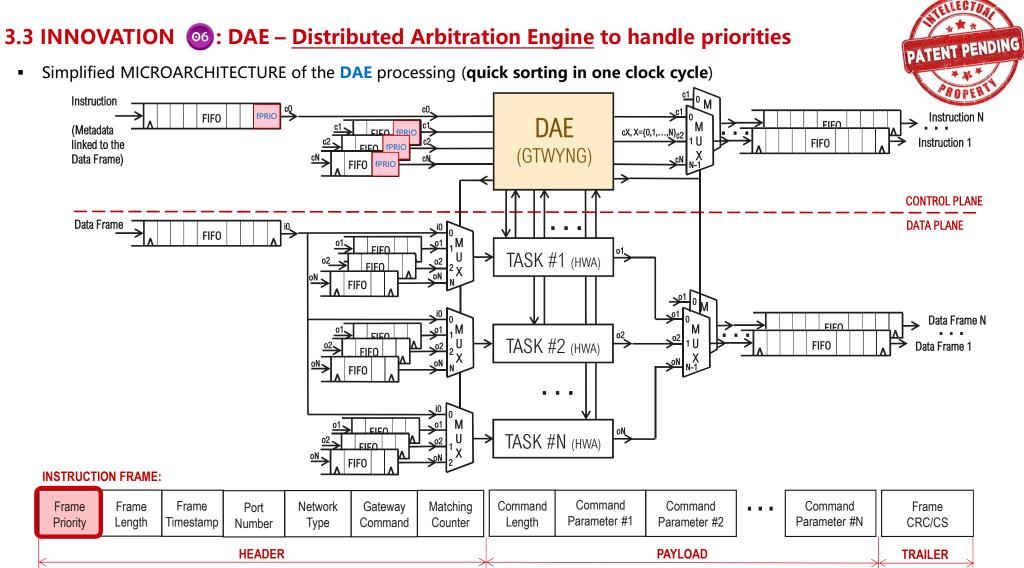

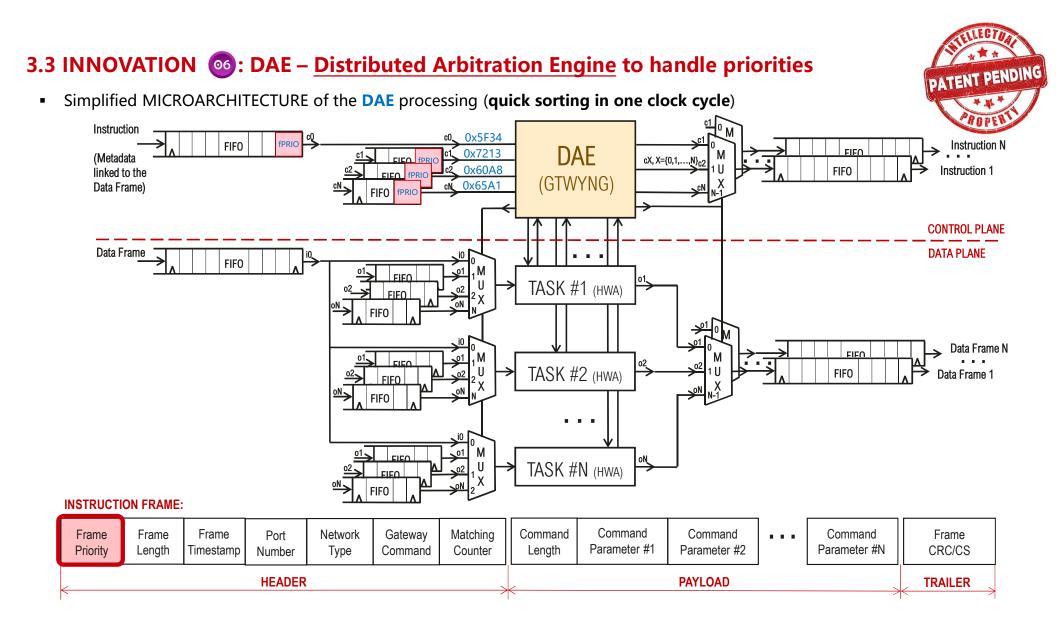

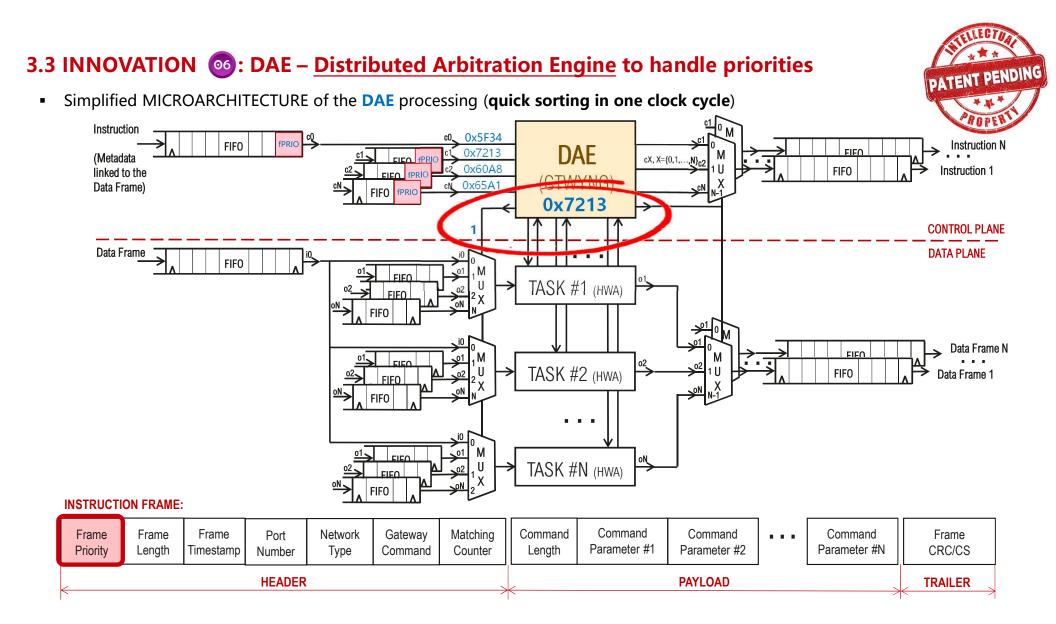

- As arbitration strategy, the first and foremost relevant field of the instruction frame (FramePRIO) defines the priority (insight from CAN carrier sense multiple access / Collision Detection CSMA/CD). Many factors take part in the inline priority assignment per frame, for instance compacted in a 16-bits word:

- Highest priority [1bit: interrupt]

- Queue status [1bit: (nearly) full, (nearly) empty]

- Timeout/timestamp [4bits: time factor]

- Tasks/HWAs status [2bits: free, free2taken, taken2free, taken]

- Shaper status [2bits: free, free2use, use2free, in use]

- VLAN tag priority [3bits: level]

- FramePRIO FrameID In-band telemetry status [3bits: counter] Frame Frame Frame Port Network Gateway Matching Command Command Command Command Command Priority Length Timestamp Number Type Command Counter Length Parameter #1 Parameter #2 Parameter #N CRC/CS HEADER PAYLOAD TRAILER FramePRIO field breakdown: b15 b14 b13 b12 b11 b10 b09 b08 b07 b06 b05 b04 b03 b02 b01 b00 TK[1] TK[0] SH[1] SH[0] VL[2] HP[0] QE[0] TM[3] TM[2] TM[1] TM[0] VL[1] VL[0] IT[2] IT[1] IT[0] **FramePRIO**

**<u>Rationale</u>**: The priority of each frame is **updated on the fly** in order to adapt its priority to each moment (**time-dependent solution**, i.e, taking into account timing factors like expiration timeouts or DDS timing requirements like latency budget, delivery time, etc.)

62 Huawei Confidential

#### INSTRUCTION FRAME (NORMALIZATION):

PATENT PENDING

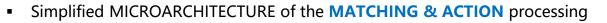

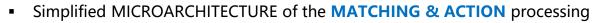

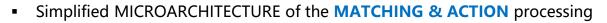

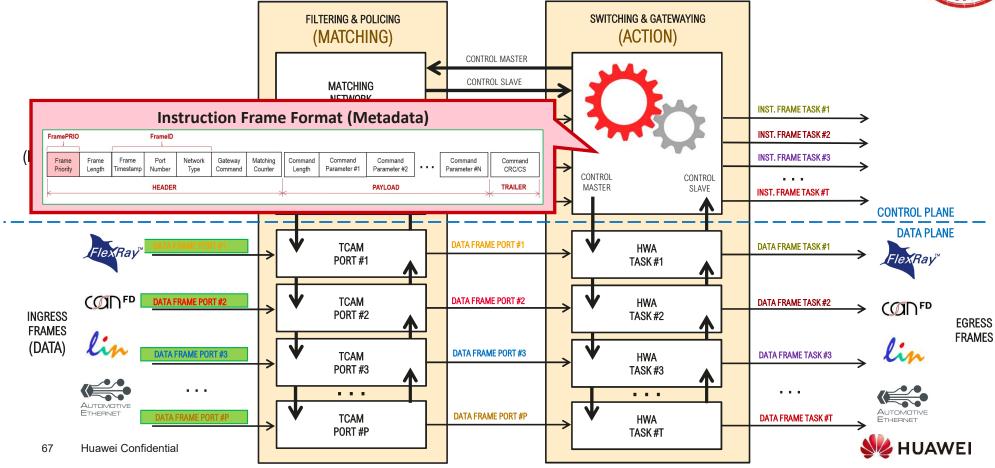

Simplified MICROARCHITECTURE of the MATCHING & ACTION processing

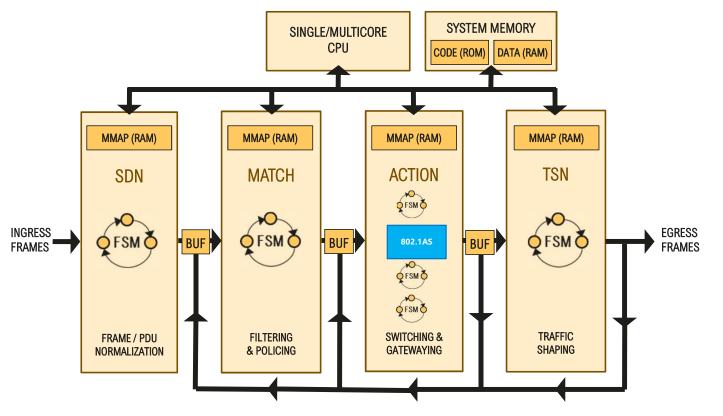

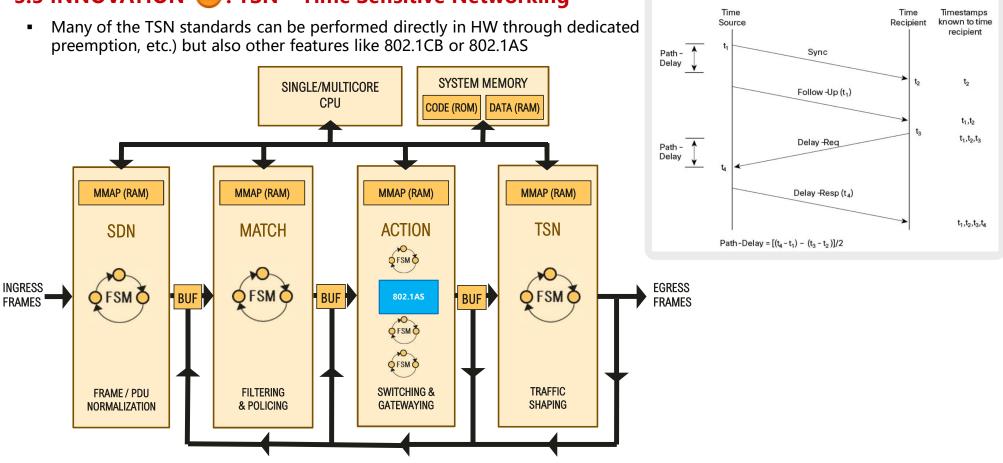

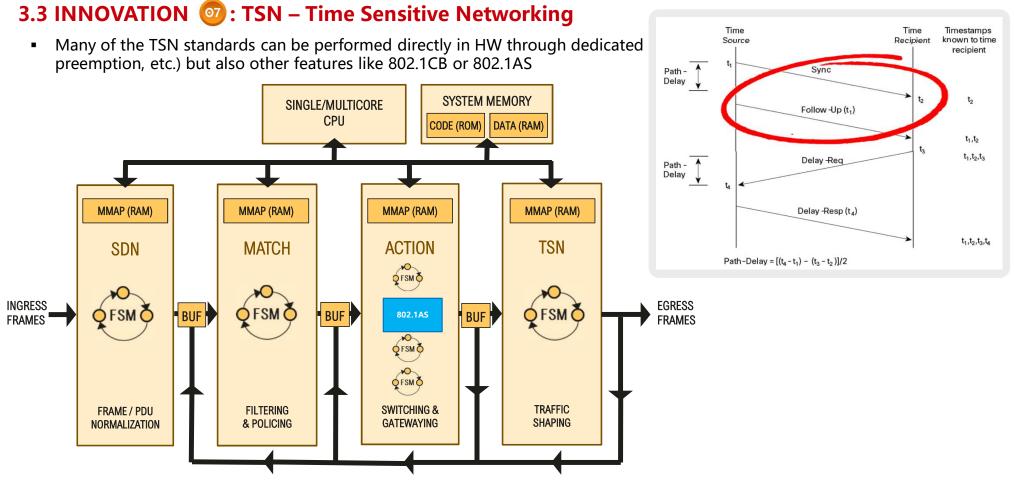

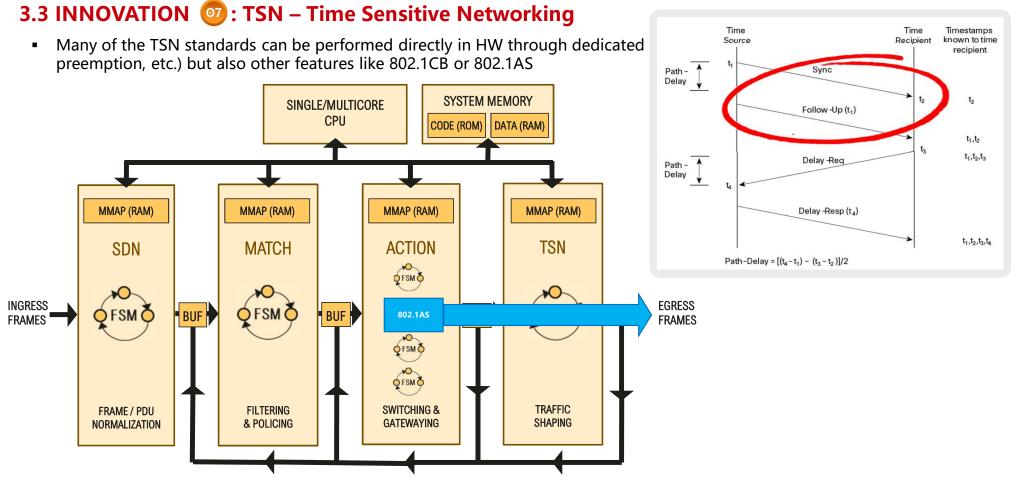

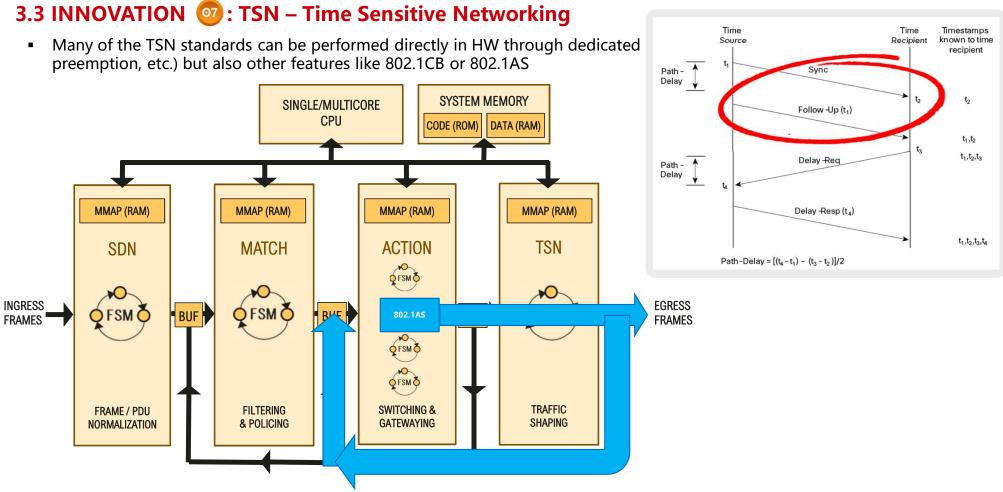

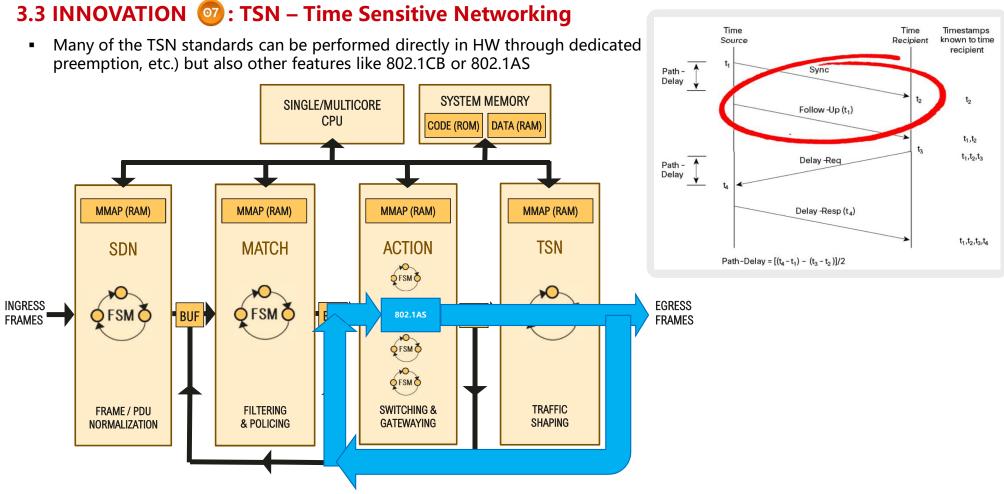

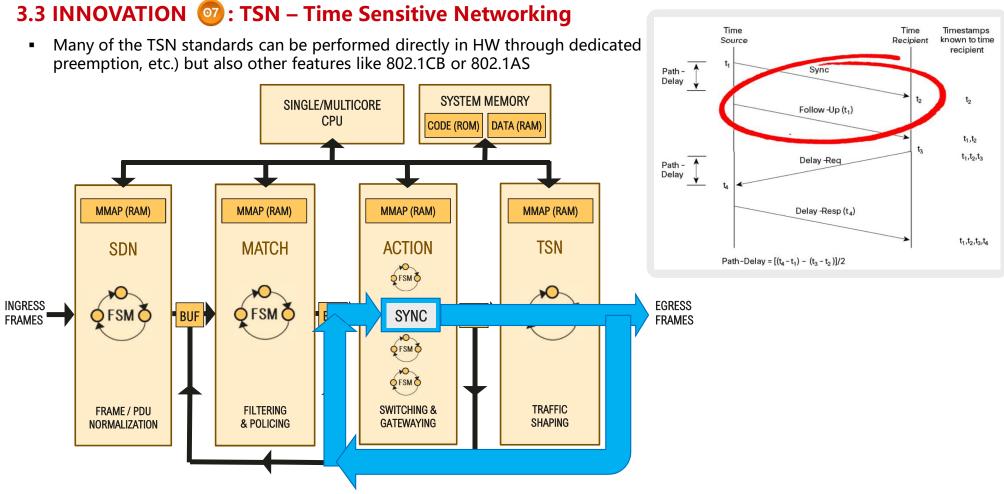

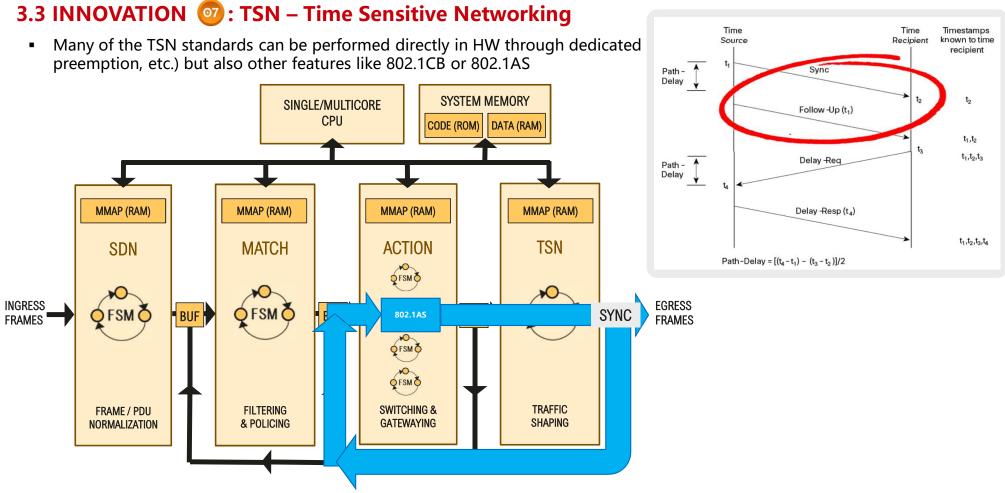

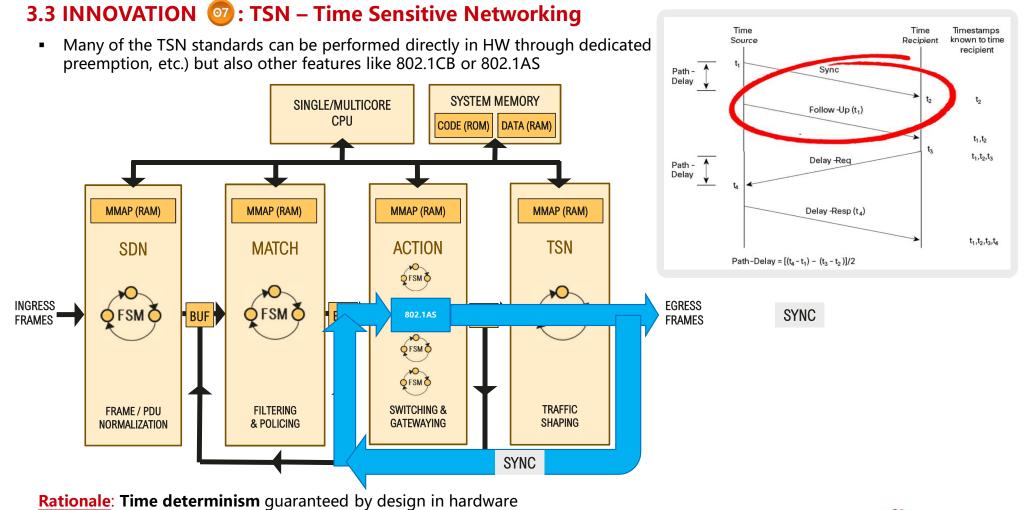

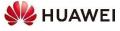

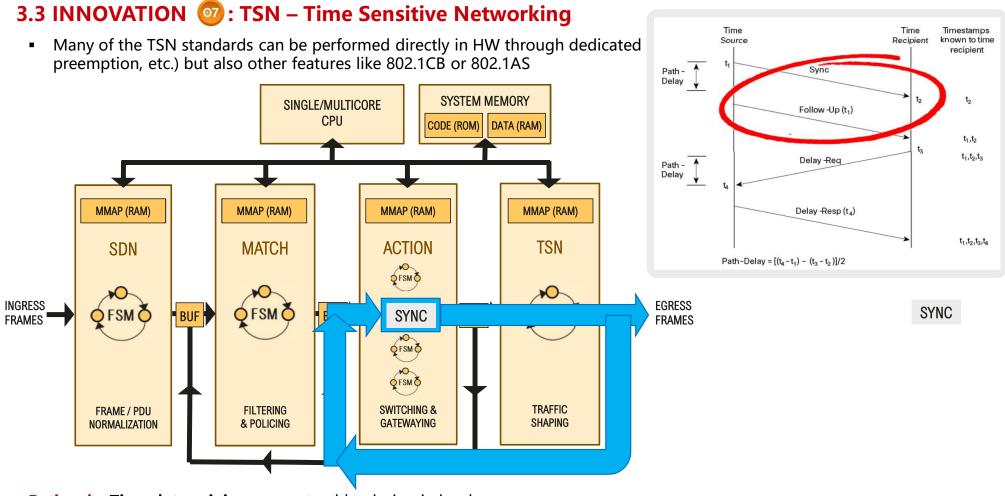

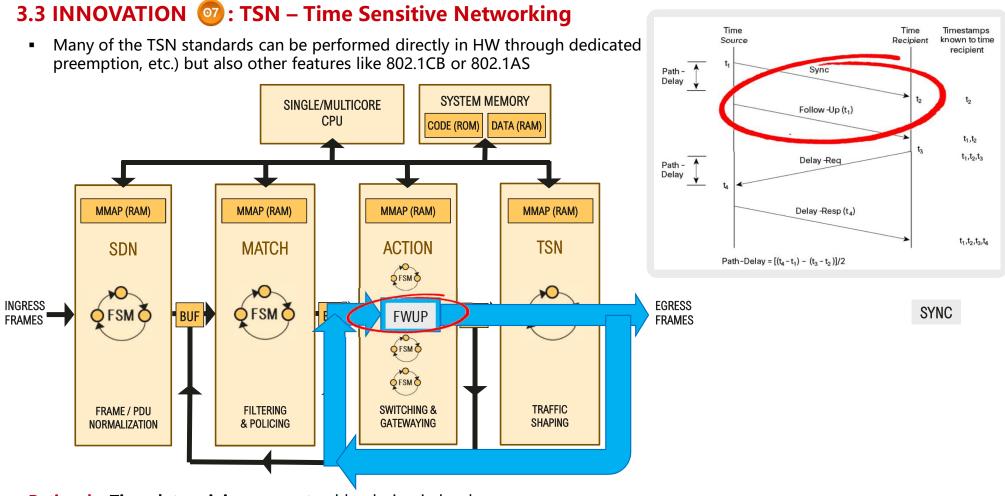

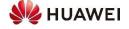

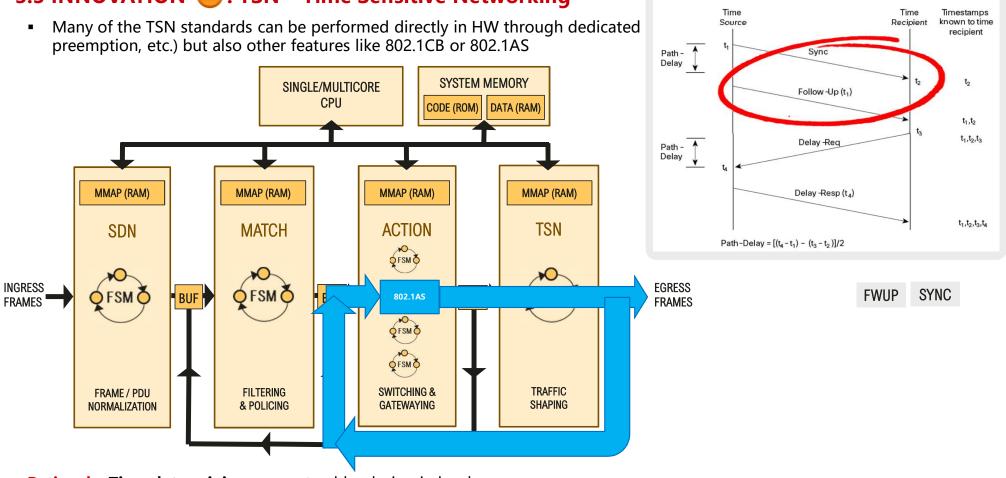

### 3.3 INNOVATION 2: TSN – Time Sensitive Networking

Many of the TSN standards can be performed directly in HW through dedicated engines, not only traffic shaping (e.g. TAS, CBS, preemption, etc.) but also other features like 802.1CB or 802.1AS

Example: Servo system

All the ECUs in the IVN need to share a common notion of time (gPTP, TSN 802.1AS)

**<u>Rationale</u>**: Time determinism guaranteed by design in hardware

### 3.3 INNOVATION 🞯 : TSN – Time Sensitive Networking

Many of the TSN standards can be performed directly in HW through dedicated engines, not only traffic shaping (e.g. TAS, CBS, preemption, etc.) but also other features like 802.1CB or 802.1AS

Rationale: Time determinism guaranteed by design in hardware

### 3.3 INNOVATION 🞯 : TSN – Time Sensitive Networking

Many of the TSN standards can be performed directly in HW through dedicated engines, not only traffic shaping (e.g. TAS, CBS, preemption, etc.) but also other features like 802.1CB or 802.1AS

Rationale: Time determinism guaranteed by design in hardware

### 3.3 INNOVATION 2: TSN – Time Sensitive Networking

Many of the TSN standards can be performed directly in HW through dedicated engines, not only traffic shaping (e.g. TAS, CBS, preemption, etc.) but also other features like 802.1CB or 802.1AS

Rationale: Time determinism guaranteed by design in hardware

# 3.3 INNOVATION 2: TSN – Time Sensitive Networking

Rationale: Time determinism guaranteed by design in hardware

#### Huawei Confidential

87

### 3.3 INNOVATION 2: TSN – Time Sensitive Networking

Rationale: Time determinism guaranteed by design in hardware

3.3 INNOVATION 1: TSN – Time Sensitive Networking

Rationale: Time determinism guaranteed by design in hardware

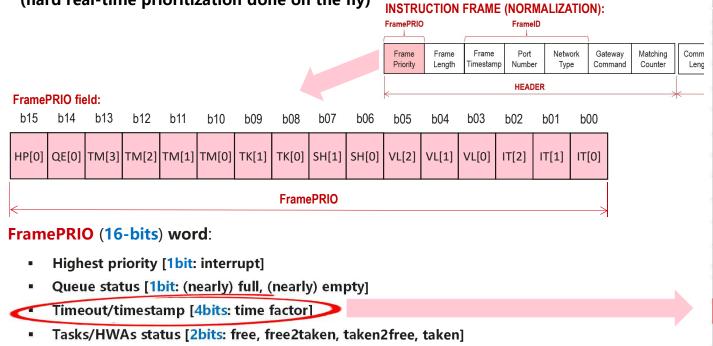

### 3.3 INNOVATION 2: DDS – Data Distribution Service deployed in Hardware

DDS middleware (data-centric Publish-Subscribe model) supported directly in HW, e.g. optimized time handling (hard real-time prioritization done on the fly)

| 1                |           |       |       |       |       |       |       |       |                | ino more non manie (normalization). |                 |                    |       |                 |                   |  |                   |                         |                         |         |                         |                   |  |  |  |

|------------------|-----------|-------|-------|-------|-------|-------|-------|-------|----------------|-------------------------------------|-----------------|--------------------|-------|-----------------|-------------------|--|-------------------|-------------------------|-------------------------|---------|-------------------------|-------------------|--|--|--|

| F                |           |       |       |       |       |       |       |       |                | FramePRIO FrameID                   |                 |                    |       |                 |                   |  |                   |                         |                         |         |                         |                   |  |  |  |

|                  |           |       |       |       |       |       |       |       |                | Frame<br>Priority                   | Frame<br>Length | Frame<br>Timestarr |       | Netwo<br>r Type | k Gatewa<br>Comma |  | Command<br>Length | Command<br>Parameter #1 | Command<br>Parameter #2 | ]       | Command<br>Parameter #N | Command<br>CRC/CS |  |  |  |

| FramePRIO field: |           |       |       |       |       |       |       | <     | HEADER PAYLOAD |                                     |                 |                    |       |                 |                   |  | PAYLOAD           |                         | >                       | TRAILER | ×                       |                   |  |  |  |

| b15              | b14       | b13   | b12   | b11   | b10   | b09   | b08   | b07   | b06            | b05                                 | b04             | b03                | b02   | b01             | b00               |  |                   |                         |                         |         |                         |                   |  |  |  |

| HP[0]            | QE[0]     | TM[3] | TM[2] | TM[1] | TM[0] | ТК[1] | тк[0] | SH[1] | SH[0]          | VL[2]                               | VL[1]           | VL[0]              | IT[2] | IT[1]           | IT[0]             |  |                   |                         |                         |         |                         |                   |  |  |  |

| <                | FramePRIO |       |       |       |       |       |       |       |                |                                     |                 | >                  |       |                 |                   |  |                   |                         |                         |         |                         |                   |  |  |  |

#### FramePRIO (16-bits) word:

- Highest priority [1bit: interrupt]

- Queue status [1bit: (nearly) full, (nearly) empty]

- Timeout/timestamp [4bits: time factor]

- Tasks/HWAs status [2bits: free, free2taken, taken2free, taken]

- Shaper status [2bits: free, free2use, use2free, in use]

- VLAN tag priority [3bits: level]

- In-band telemetry status [3bits: counter]

#### Rationale: Quality-of-Service (QoS) policies guaranteed by design in hardware (e.g. time and priority handling)

## 3.3 INNOVATION 2: DDS – Data Distribution Service deployed in Hardware

DDS middleware (data-centric Publish-Subscribe model) supported directly in HW, e.g. optimized time handling (hard real-time prioritization done on the fly)

| •             |                  |       |       |       |       |       |       |       |           | INSTRUCTION FRAME (NORMALIZATION). |                 |                    |               |                  |         |  |                      |                   |                         |                         |   |                         |                   |  |  |  |

|---------------|------------------|-------|-------|-------|-------|-------|-------|-------|-----------|------------------------------------|-----------------|--------------------|---------------|------------------|---------|--|----------------------|-------------------|-------------------------|-------------------------|---|-------------------------|-------------------|--|--|--|

| <b>F</b><br>۲ |                  |       |       |       |       |       |       |       | FramePRIC | iramePRIO FrameID                  |                 |                    |               |                  |         |  |                      |                   |                         |                         |   |                         |                   |  |  |  |

|               |                  |       |       |       |       |       |       |       |           | Frame<br>Priority                  | Frame<br>Length | Frame<br>Timestarr | Port<br>Numbe | Netwo<br>er Type | 10000 C |  | /latching<br>Counter | Command<br>Length | Command<br>Parameter #1 | Command<br>Parameter #2 | ] | Command<br>Parameter #N | Command<br>CRC/CS |  |  |  |

| FrameP        | FramePRIO field: |       |       |       |       |       |       |       | <         | HEADER RAYLOAD                     |                 |                    |               |                  |         |  |                      |                   | ;                       | TRAILER                 | × |                         |                   |  |  |  |

| b15           | b14              | b13   | b12   | b11   | b10   | b09   | b08   | b07   | b06       | b05                                | b04             | b03                | b02           | b01              | b00     |  |                      |                   |                         |                         |   |                         |                   |  |  |  |

| HP[0]         | QE[0]            | TM[3] | TM[2] | TM[1] | TM[0] | TK[1] | тк[0] | SH[1] | SH[0]     | VL[2]                              | VL[1]           | VL[0]              | IT[2]         | IT[1]            | IT[0]   |  |                      |                   |                         |                         |   |                         |                   |  |  |  |

| <             | FramePRIO        |       |       |       |       |       |       |       |           |                                    |                 |                    |               |                  |         |  |                      |                   |                         |                         |   |                         |                   |  |  |  |

#### FramePRIO (16-bits) word:

- Highest priority [1bit: interrupt]

- Queue status [1bit: (nearly) full, (nearly) empty]

- Timeout/timestamp [4bits: time factor]

- Tasks/HWAs status [2bits: free, free2taken, taken2free, taken]

- Shaper status [2bits: free, free2use, use2free, in use]

- VLAN tag priority [3bits: level]

- In-band telemetry status [3bits: counter]

#### Rationale: Quality-of-Service (QoS) policies guaranteed by design in hardware (e.g. time and priority handling)

94 Huawei Confidential

PATENT PENDI

TABLE 1. Supported QoS policies of DDS version 1.4

# 3.3 INNOVATION 2: DDS – Data Distribution Service deployed in Hard

DDS middleware (data-centric Publish-Subscribe model) supported directly in HW, e.g. optim (hard real-time prioritization done on the fly)

- Shaper status [2bits: free, free2use, use2free, in use]

- VLAN tag priority [3bits: level]

- In-band telemetry status [3bits: counter]

#### Rationale: Quality-of-Service (QoS) policies guaranteed by design in hardware (e.g. time and p

95 Huawei Confidential

| QoS policy                | Description                                                                                      | DataReader | DataWriter | DomainParticinant | Publisher | Subscriber | Tonic |

|---------------------------|--------------------------------------------------------------------------------------------------|------------|------------|-------------------|-----------|------------|-------|

| USER_DATA                 | Custom user data                                                                                 | X          | x          |                   |           |            |       |

| TOPIC_DATA                | Custom user data                                                                                 | 2          | 100        | 1                 |           | 2          | х     |

| GROUP_DATA                | Custom user data                                                                                 |            |            | - 22              | х         | x          |       |

| DURABILITY                | If data should "outlive" their writing time (e.g. late-joining DataReaders) <sup>abc</sup>       | x          | x          |                   |           |            | x     |

| DURABILITY_<br>SERVICE    | Specifies the service implementing the<br>durability (if any) <sup>b</sup>                       |            | X          |                   |           |            | x     |

| PRESENTATION              | How changes to data are presented to subscribing applications <sup>abc</sup>                     |            |            |                   | X         | X          |       |

| DEADLINE                  | Maximum time after which DataReader<br>expects an update of periodic data <sup>ac</sup>          | X          | X          |                   |           |            | x     |

| LATENCY_<br>BUDGET        | Maximum delay from data write to data<br>reception and notification <sup>ac</sup>                | x          | X          | 2                 | - 3       |            | x     |

| OWNERSHIP                 | If multiple DataWriters can write the same data instance <sup>abc</sup>                          | x          | X          |                   |           |            | x     |

| OWNERSHIP_<br>STRENGTH    | Strength of the DataWriter for arbitration<br>in case of exclusive OWNERSHIP <sup>c</sup>        |            | x          | - 6               |           |            |       |

| LIVELINESS                | Mechanism to determine if an entity is active ("alive") <sup>abc</sup>                           | x          | X          | 0                 |           |            | x     |

| TIME_BASED_<br>FILTER     | Minimum time a DataReader is<br>interested in receiving updates                                  | x          |            | 6                 |           | 5          |       |

| PARTITION                 | Logical partition among the topics visi-<br>ble by the Publisher and the Subscriber <sup>c</sup> |            | 6753       | 52                | X         | X          | 022   |

| RELIABILITY               | Reliability level of message delivery <sup>abc</sup>                                             | x          | x          | 25                |           | -          | x     |

| TRANSPORT_<br>PRIORITY    | Priority to be used on underlying<br>transport <sup>c</sup>                                      |            | x          | 1                 |           | 5          | x     |

| LIFESPAN                  | Maximum time of validity of written<br>data, to avoid delivery of "stale" data <sup>c</sup>      |            | X          | -3                |           |            | х     |

| DESTINATION_<br>ORDER     | Logical order among changes made by<br>Publishers to the same data instance <sup>abc</sup>       | х          | X          |                   |           |            | x     |

| HISTORY                   | Behavior in case a sample changes be-<br>fore being communicated <sup>b</sup>                    | x          | X          | 99                |           | 5          | X     |

| RESOURCE_<br>LIMITS       | Maximum amount of resources<br>consumed by the service <sup>b</sup>                              | x          | X          | -55               |           | -          | x     |

| ENTITY_<br>FACTORY        | Behavior of an entity when creating<br>other entities                                            |            | 5.22       | x                 | x         | x          |       |

| WRITER_DATA_<br>LIFECYCLE | Behavior of DataWriter with respect to<br>the lifecycle of the data-instances                    |            | X          | 0                 | -         | -          | -     |

| READER_DATA_<br>LIFECYCLE | Behavior of DataReader with respect to<br>the lifecycle of the data-instances                    | x          |            | 6                 | <u> </u>  | -          |       |

<sup>a</sup> Values on the publishing and subscribing sides must be compatible.

<sup>b</sup> Not changeable.

<sup>c</sup> May appear as in-line QoS inside RTPS messages.

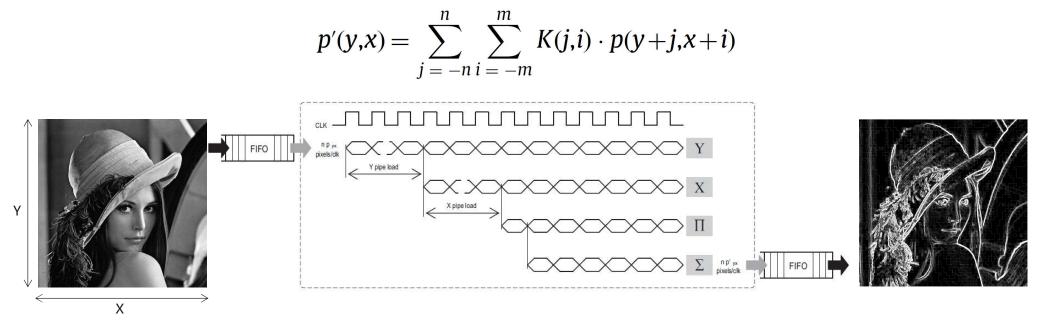

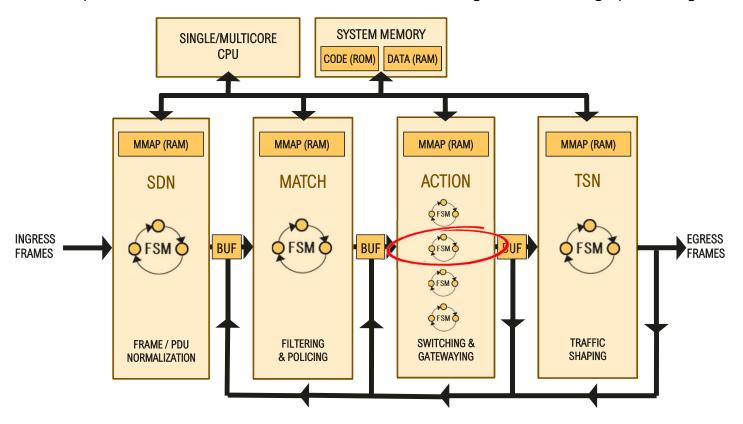

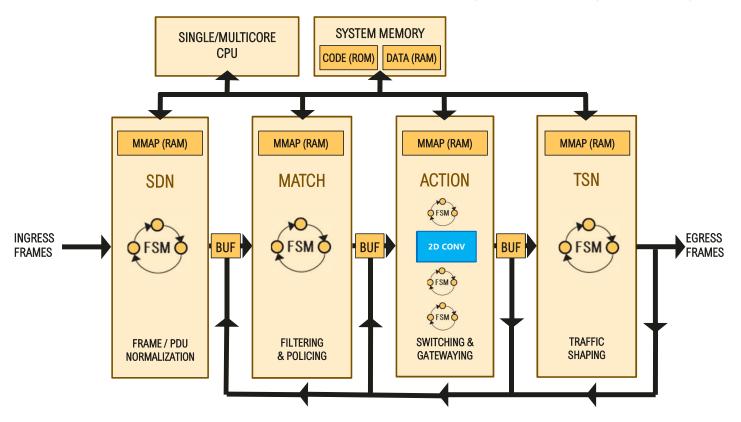

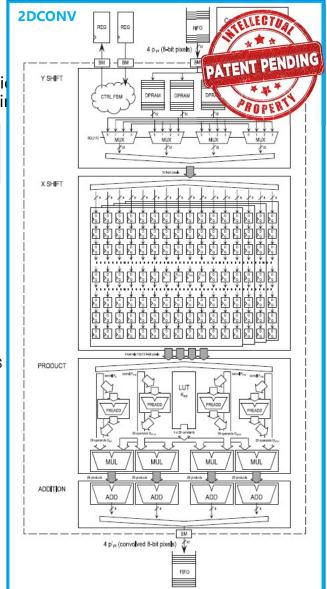

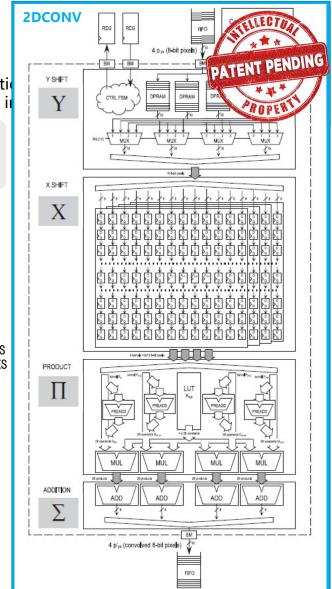

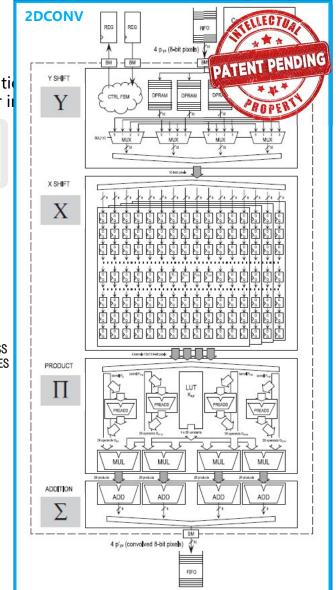

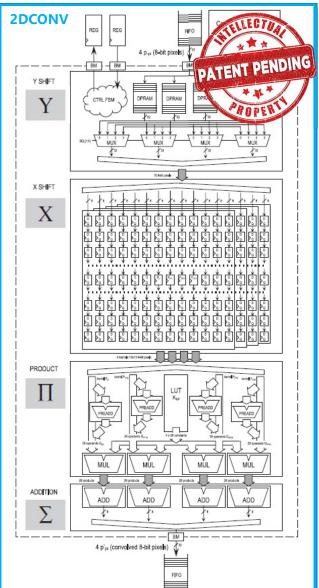

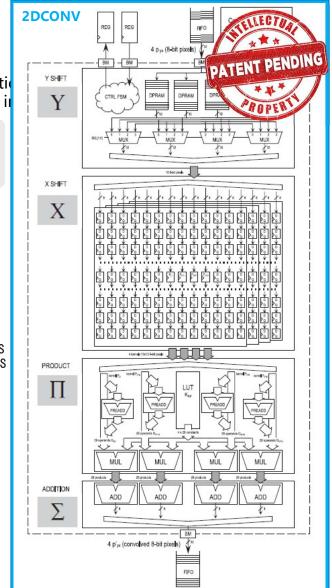

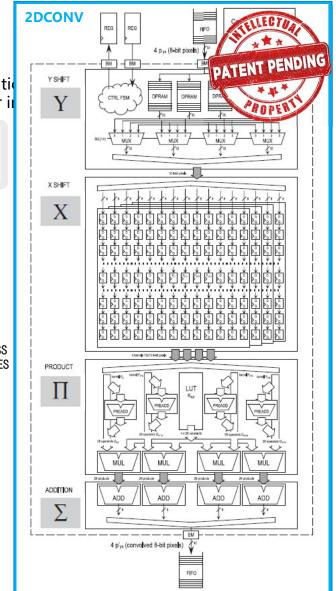

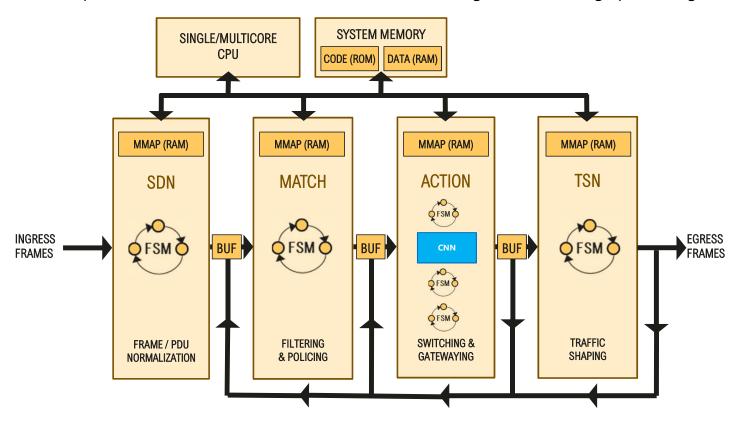

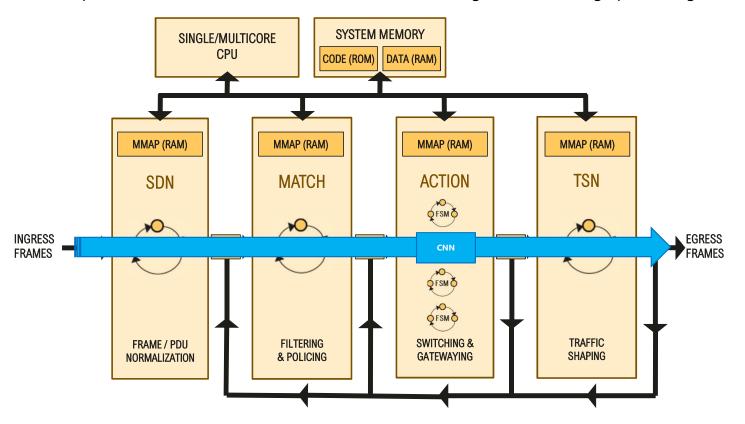

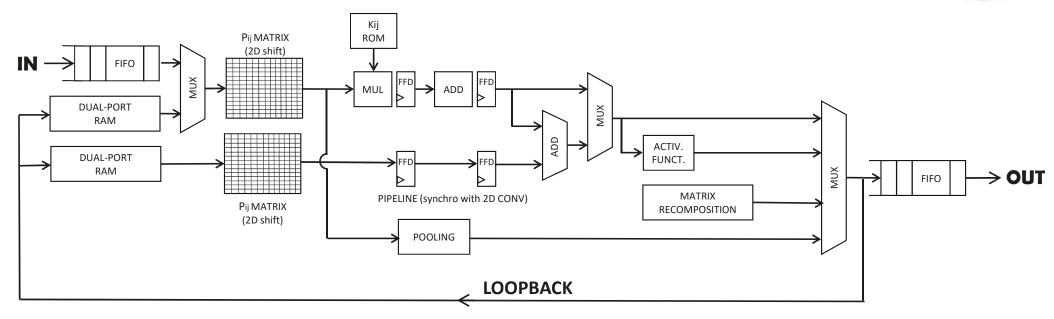

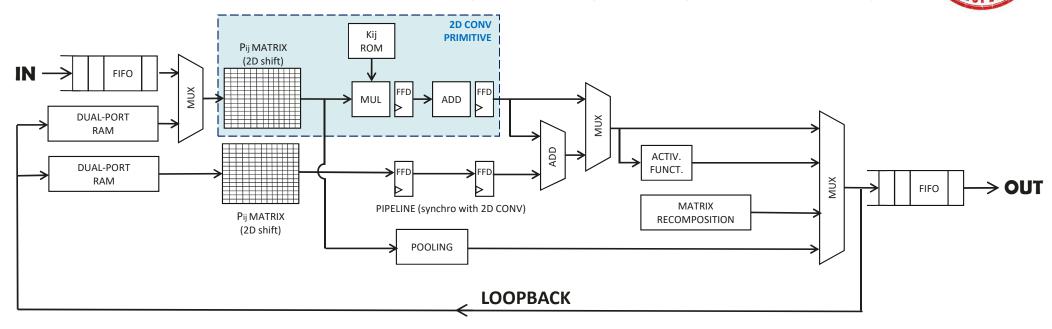

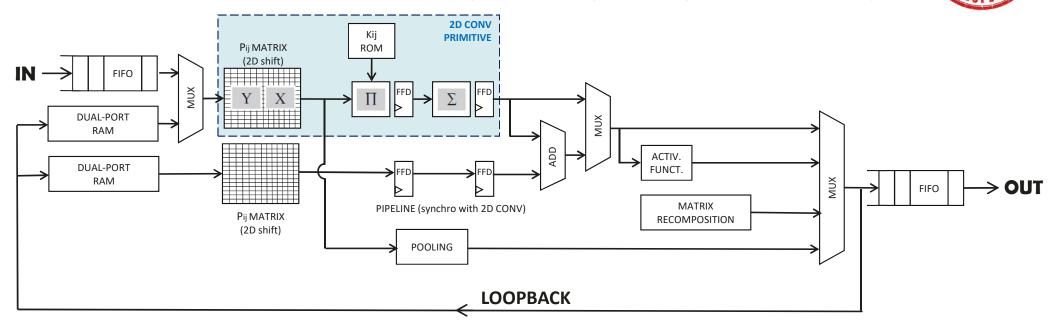

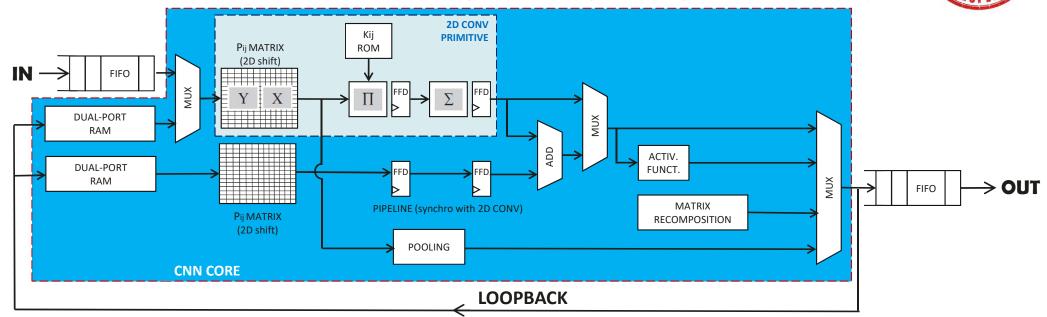

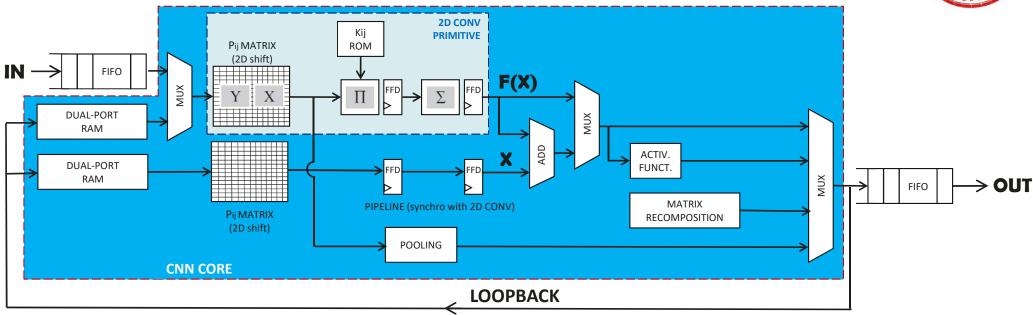

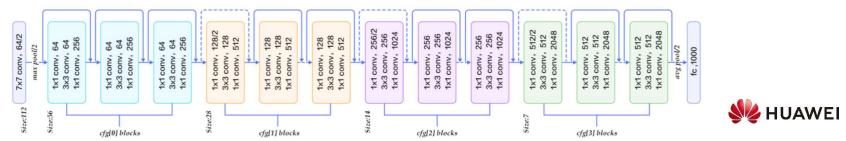

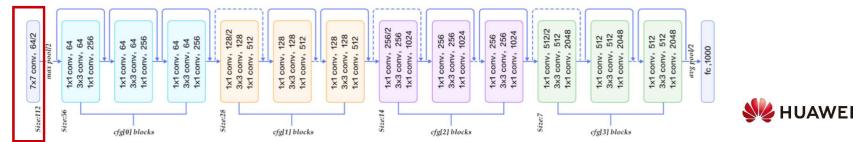

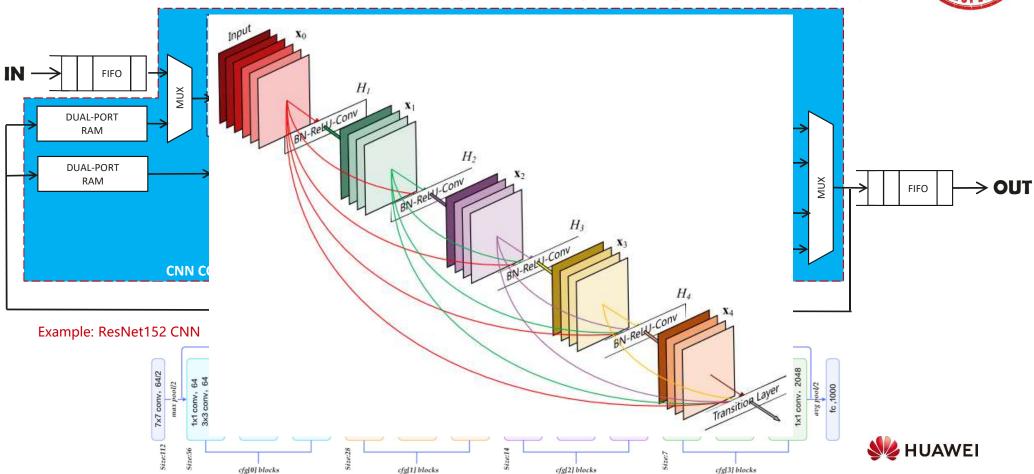

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### **<u>Rationale</u>**: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

**<u>Rationale</u>**: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

**<u>Rationale</u>**: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

# **<u>Rationale</u>**: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution as part of a convolutional neural network (CNN) HW engine used in image processing or in

**<u>Rationale</u>**: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Rationale: Effective spatial processing doing it inline and in-memory

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

PATENT PENDING

\* # \*

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

PATENT PENDING

\* # \*

PATENT PENDING It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (**2DCONV**) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

\* # \*

It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (2DCONV) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

#### Example: ResNet152 CNN

PATENT PENDING It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (**2DCONV**) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

\* # \*

#### Example: ResNet152 CNN

PATENT PENDING It is possible to design custom HWAs for specific applications, e.g. instance a 2D convolution (**2DCONV**) HW engine as part of a convolutional neural network (CNN) HW engine used in image processing or intrusion detection system

Zonal Gateway Controllers demand certain functionalities that shall be adapted at run-time based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- Stateful Firewall: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- Network Intrusion Detection System (NIDS): Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be **adapted at run-time** based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- <u>Stateful Firewall</u>: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- <u>Network Intrusion Detection System (NIDS)</u>: Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system

HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be adapted at run-time based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- Stateful Firewall: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- Network Intrusion Detection System (NIDS): Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be adapted at run-time based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- Stateful Firewall: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- Network Intrusion Detection System (NIDS): Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be adapted at run-time based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- Stateful Firewall: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- Network Intrusion Detection System (NIDS): Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be adapted at run-time based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- Stateful Firewall: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- Network Intrusion Detection System (NIDS): Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system HUAWEI

Zonal Gateway Controllers demand certain functionalities that shall be **adapted at run-time** based on specific environmental conditions or events triggered at real-time. Our **SoC modular architecture** enables it. Some use cases are:

- Access Control List (ACL): Add/Remove/Change ACL rules on the fly, e.g. system update at run-time

- <u>Stateful Firewall</u>: Add/Remove/Change firewall rules and state-based FSM at run-time, e.g. response to traffic congestion

- <u>Network Intrusion Detection System (NIDS)</u>: Add/Remove/Change Intrusion Detection rules on the fly in response to an attack

Rationale: Self-adaptive response at run-time, i.e., on the fly, without interrupting the operation of the cyber-physical system

HUAWEI

**<u>Rationale</u>**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

**<u>Rationale</u>**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

#### **Rationale**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability Huawei Confidential

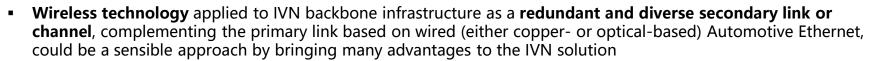

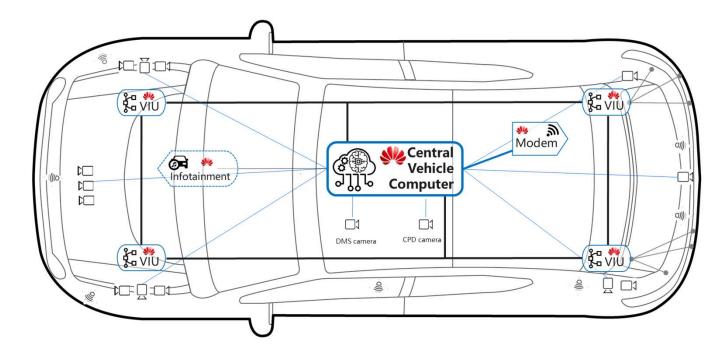

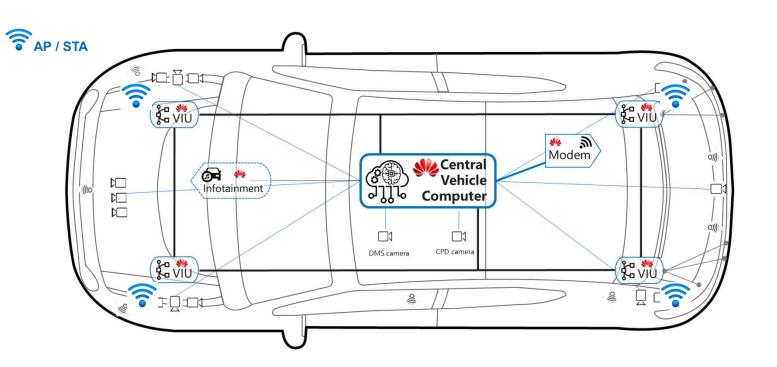

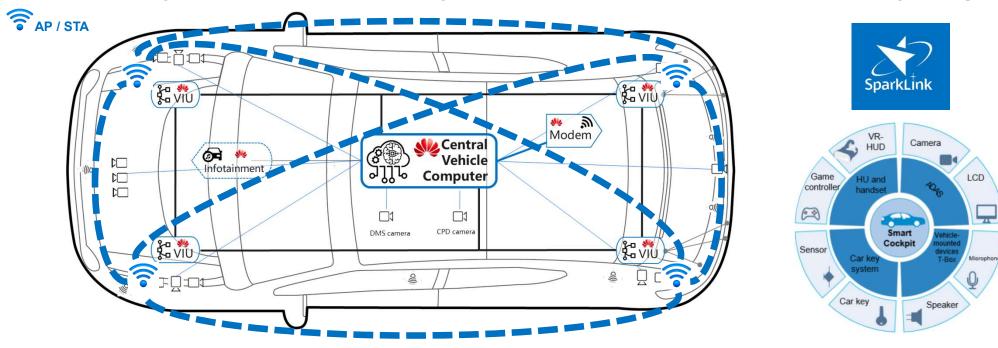

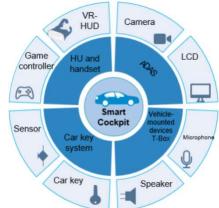

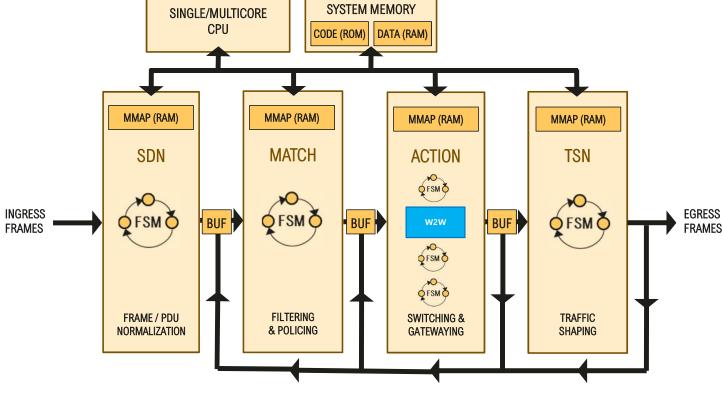

Wireless technology applied to IVN backbone infrastructure as a redundant and diverse secondary link or channel, complementing the primary link based on wired (either copper- or optical-based) Automotive Ethernet, could be a sensible approach by bringing many advantages to the IVN solution

#### Trustworthy (Redundant & Diverse) Hybrid "Wired+Wireless" IVN Infrastructure by Design!

#### **Rationale**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability 129 Huawei Confidential

#### *Trustworthy (Redundant & Diverse) Hybrid "Wired+Wireless" IVN Infrastructure by Design!*

**<u>Rationale</u>**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

131

SparkLink

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability Huawei Confidential

**Rationale**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

SparkLink

Smart Cockpit

Camera

Dyo

Speaker

LCD

<u>\_</u>

Microph

VR-

HUD

HU and

hand

Car ke

Car key

system

Game

controller

(2)

Sensor

**Rationale**: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

Wireless technology applied to IVN backbone infrastructure as a redundant and diverse secondary link or channel, complementing the primary link based on wired (either copper- or optical-based) Automotive Ethernet, could be a sensible approach by bringing many advantages to the IVN solution

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability Huawei Confidential 134

SparkLink VR-Camera HUD Game LCD HU and Por controller hand <u>\_</u> (2) Smart Cockpit Sensor Car ke Microph system Car key Speaker

Wireless technology applied to IVN backbone infrastructure as a redundant and diverse secondary link or channel, complementing the primary link based on wired (either copper- or optical-based) Automotive Ethernet, could be a sensible approach by bringing many advantages to the IVN solution

Rationale: Effective balance of high-performance, flexibility/versatility, modularity/reusability and scalability

135 Huawei Confidential

SparkLink

Smart Cockpit

Camera

Dyo

Speaker

LCD

<u>\_</u>

Microph

VR-

HUD

HU and

hand

Car ke

Car key

system

Game

controller

(2)

Sensor

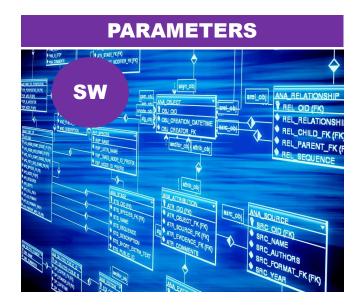

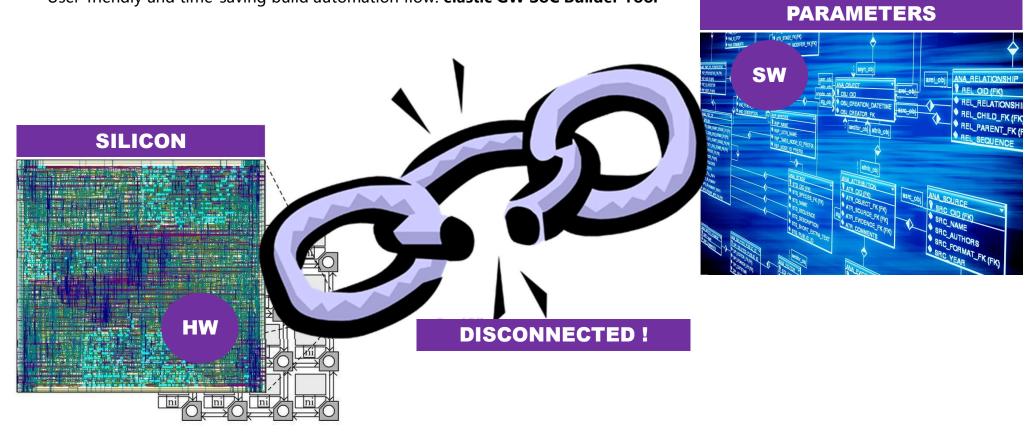

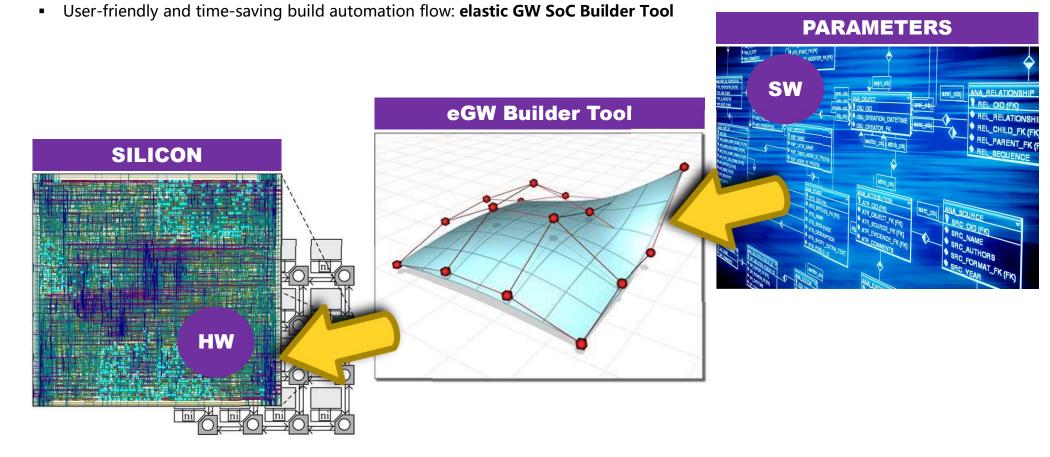

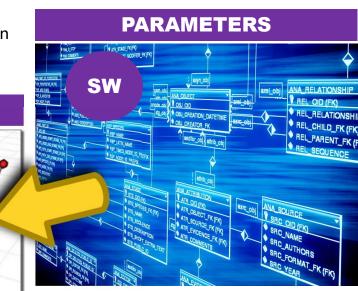

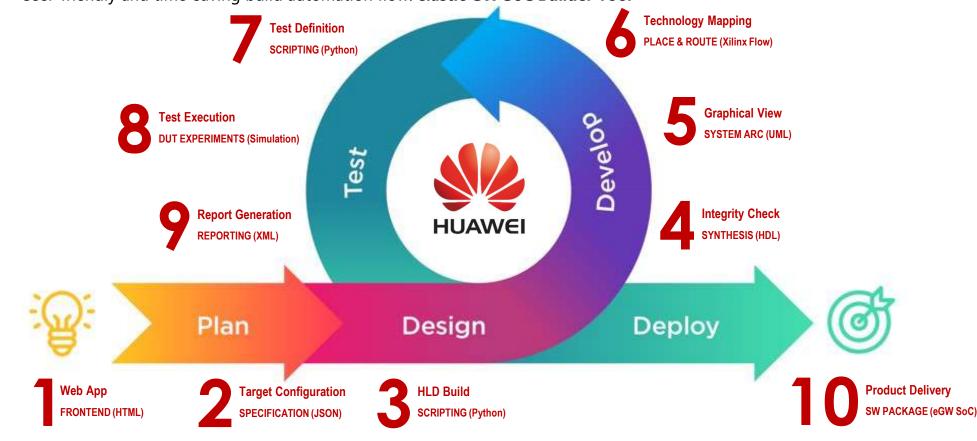

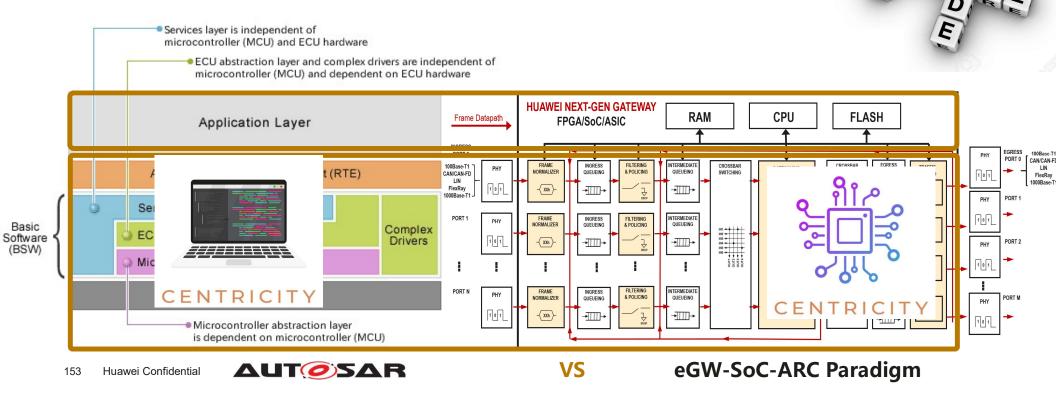

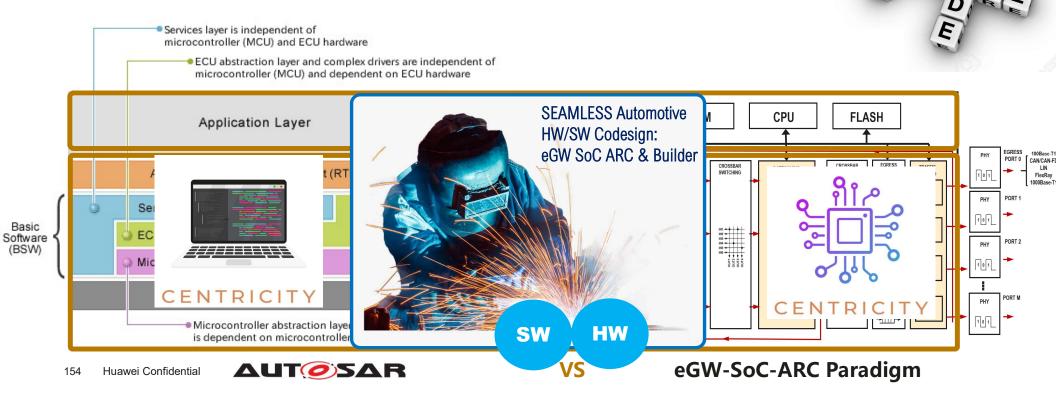

• User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

#### **<u>Rationale</u>**: Automated elastic SoC design methodology based on system parameters exploited at low level

• User-friendly and time-saving build automation flow: **elastic GW SoC Builder Tool**

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

**eGW Builder Tool**

User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

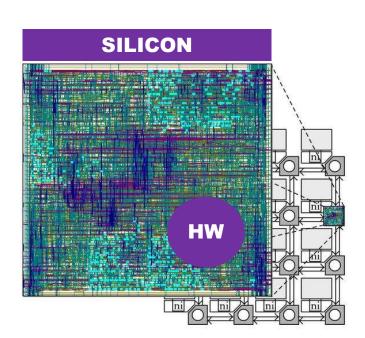

Our **Core Technology**: **Library of ultra-parameterized IP Cores (HWA)** to enable an extremely flexible low level abstraction able to address SoC design aspects like:

- Geometry (number ingress/egress ports, etc.) and shape (memory, size, wide, etc.)

- IO interface (bus size, wide, etc.)

SILICON

Functionality inside (feature #1, #2,... #N)

HW

#### **<u>Rationale</u>**: Automated elastic SoC design methodology based on system parameters exploited at low level

- User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

Our Core Technology: Library of ultra-parameterized IP Cores (HWA) to enable an extremely flexible low level abstraction able to address SoC design aspects like:

- Geometry (number ingress/egress ports, etc.) and shape (memory, size, wide, etc.)

- IO interface (bus size, wide, etc.)

SILICON

• Functionality inside (feature #1, #2,... #N)

HW

# v: elastic GW SoC Builder Tool ted IP Cores (HWA) to enable an tess SoC design aspects like: (memory, size, wide, etc.) eGW Builder Tool Core of the society of the so

From **Parameters** to **Silicon** via the instantiation of **ultra-parameterized HWAs** to eradicate complexity by shifting key functions from SW to HW

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

140 Huawei Confidential

HUAWEI

- Plan Design Deploy

- User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

Huawei Confidential

141

HUAWEI

• User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

MUAWEI

• User-friendly and time-saving build automation flow: elastic GW SoC Builder Tool

Rationale: Automated elastic SoC design methodology based on system parameters exploited at low level

#### SUMMARY – Automotive Zonal Gatewaying Solution: eGW System & Method

**RECAP**: **eGW SoC** targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

**RECAP**: eGW SoC targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

145 Huawei Confidential

**V** HUAWEI

**RECAP**: eGW SoC targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

146 Huawei Confidential

**V** HUAWEI

**RECAP**: eGW SoC targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

147 Huawei Confidential

👐 HUAWEI

**RECAP**: eGW SoC targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

**RECAP**: eGW SoC targeting Automotive Zonal GWs – 12 HW innovations on Architecture and HW Accelerators (IP cores)

149 Huawei Confidential

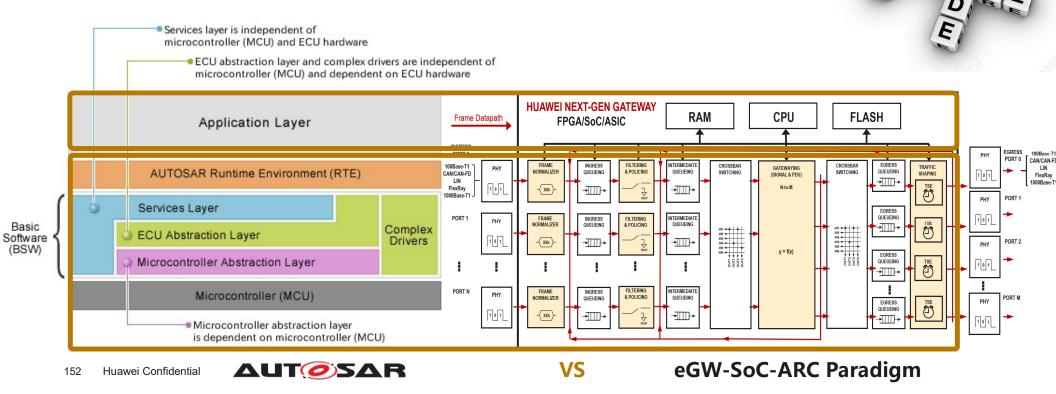

**eGW** - The **pioneer all-in-one gatewaying solution** combining <u>high-performance</u> (ultra-low latency, jitter), <u>networking</u> (SDN, TSN, DDS), <u>application</u> processing, <u>security</u> (ACL, NGFW, NIDS) and <u>safety features</u> (redundancy, self-monitoring, self-healing) driven by a **full ingress-to-egress data flow** deployed through custom **HWAs** to effectively **offload the host CPU and prune SW complexity**

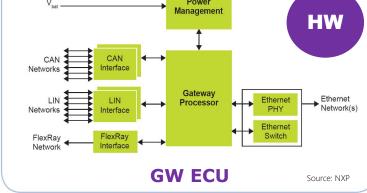

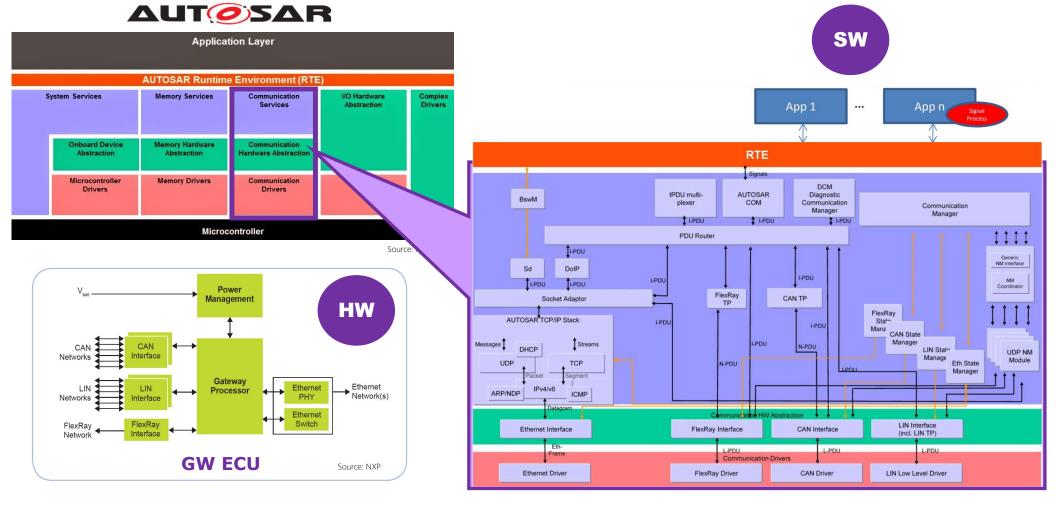

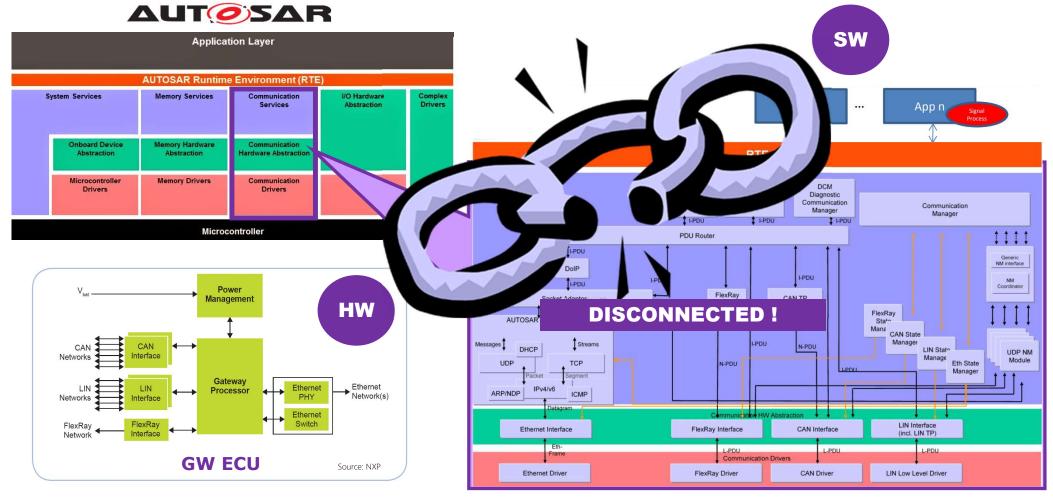

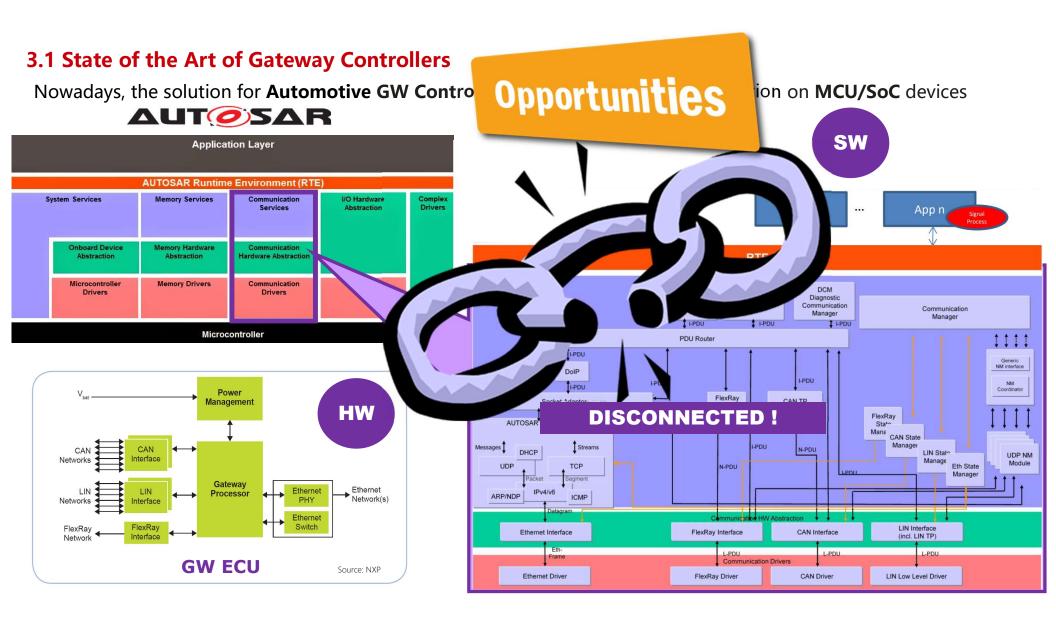

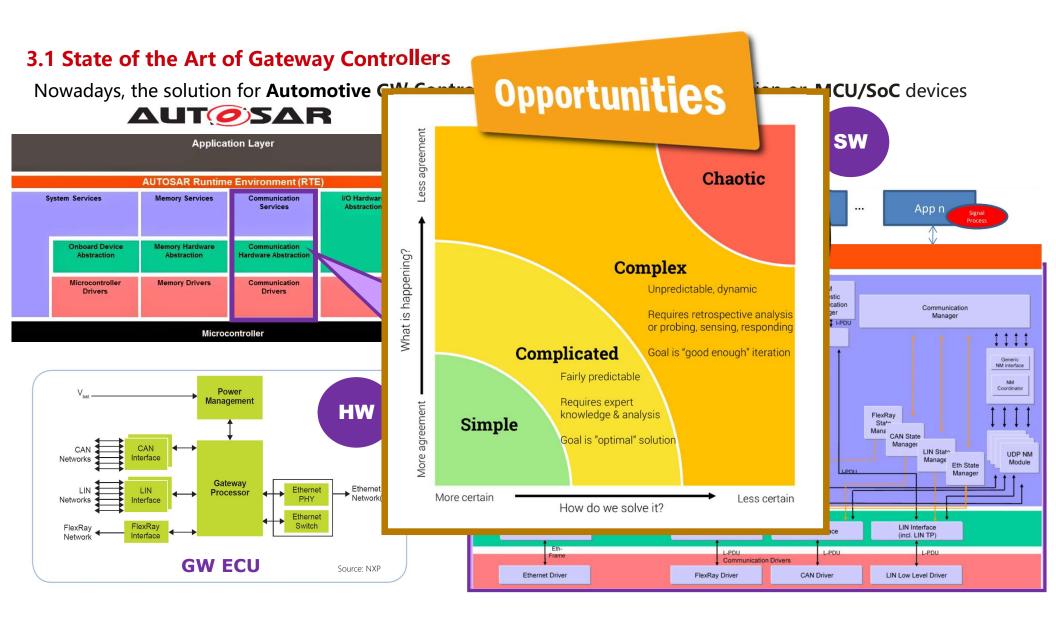

HW/SW Codesign: Synthesis of functionality distributed in SW modules & HW IP cores to shift from SW centricity to HW centricity (our proposed paradigm shift!)

Reshaping of HW/SW stacks with a new functional breakdown:

- App Layer: Host CPU (orchestration and management)

- BSW Layer: Innovative HWAs (HW-centric APP & NW Functions/Primitives)

PDA

D

HW/SW Codesign: Synthesis of functionality distributed in SW modules & HW IP cores to shift from SW centricity to HW centricity (our proposed paradigm shift!)

Reshaping of HW/SW stacks with a new functional breakdown:

- App Layer: Host CPU (orchestration and management)

- BSW Layer: Innovative HWAs (HW-centric APP & NW Functions/Primitives)

PDA

D

W

HW/SW Codesign: Synthesis of functionality distributed in SW modules & HW IP cores to shift from SW centricity to HW centricity (our proposed paradigm shift!)

Reshaping of HW/SW stacks with a new functional breakdown:

- App Layer: Host CPU (orchestration and management)

- BSW Layer: Innovative HWAs (HW-centric APP & NW Functions/Primitives)

PDA

D

W

HW/SW Codesign: Synthesis of functionality distributed in SW modules & HW IP cores to shift from SW centricity to HW centricity (our proposed paradigm shift!)

Reshaping of HW/SW stacks with a new functional breakdown:

- App Layer: Host CPU (orchestration and management)

- BSW Layer: Innovative HWAs (HW-centric APP & NW Functions/Primitives)

PDA

#### **Deliverables & Outcomes:**

- 14 Patent Applications (EU and CN)

- 8 Conference Papers

- 2 Journals (impact factor)

- 1 Master Thesis eGW Builder (Grade 1.0)

- 1 PhD Thesis eGW SoC (ongoing)

#### CONCLUSIONS

"Software Defined Vehicle (SDV) should not mean developing complex SW but implementing simple SW to configure and control reliable & smart flexible HW dedicated to high performance computing and communications."

"Because developing ACES vehicles implies to efficiently craft µs or hundreds of ns, not ms any more, at both computation and communication levels."

Francesc Fons, TUM AS 2022

158 Huawei Confidential

0101

200

00

90

001

010

# Thank you.

Dr.-Ing. Francesc Fons francesc.fons@huawei.com

Automotive IVN Research Group

Automotive Engineering Lab - Huawei Munich Research Center

159 Huawei Confidential